Introduction

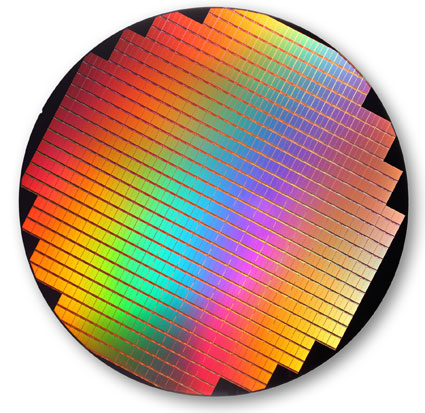

IC designs go through a layout process and then a verification of that layout to determine if the layout layer width and spacing rules conform to a set of manufacturing design rules. Adhering to the layout rules will ensure that your chip has acceptable yields.

At the 28nm node a typical DRC (Design Rule Check) deck will… Read More

Novelty-Based Methods for Random Test Selection. Innovation in VerificationCoverage improvement effectiveness through randomized testing declines as…Read More

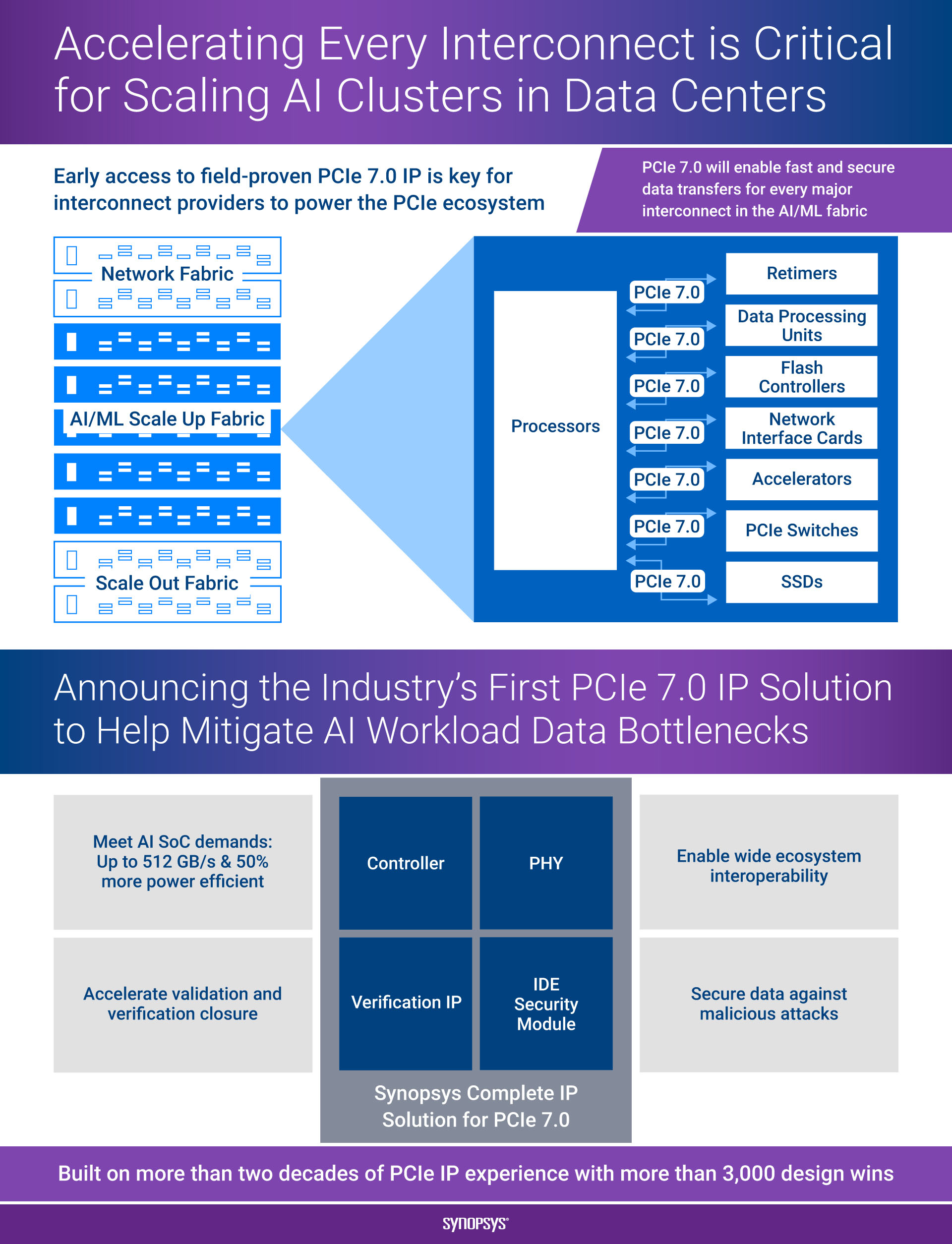

Novelty-Based Methods for Random Test Selection. Innovation in VerificationCoverage improvement effectiveness through randomized testing declines as…Read More Synopsys' Strategic Advancement with PCIe 7.0: Early Access and Complete Solution for AI and Data Center InfrastructureIn the rapidly evolving world of high-performance computing…Read More

Synopsys' Strategic Advancement with PCIe 7.0: Early Access and Complete Solution for AI and Data Center InfrastructureIn the rapidly evolving world of high-performance computing…Read MoreMentor 2 : Carl Icahn 0

The corporate raiders are still throwing rocks at Mentor Graphics. I have followed this reality show VERY closely and find their latest assault seriously counterproductive. Disinformation is common in EDA but I expected more from Carl Icahn and the Raiderettes. They are quite the drama queens. Here is a billion dollar question:… Read More

TSMC Conference Call is a 6.5 on the Richter Scale

TSMC continues to drive the economic recovery with impressive Q1 numbers and an even more impressive Q2 and Q3 outlook. TSMC is my economic bellwether due to its diverse customer base and shear volume of consumer electronics silicon. The big surprise in the 1 hour Q1 conference call is a new Giga Fab (#15) ground breaking this year… Read More

Ivo Bolsens of Xilinx and Crossover Designs

I was at Mentor’s u2u (user group) meeting and one of the keynotes was by Ivo Bolsens of Xilinx. The other was by Wally Rhines and is summarized here.

Ivo started off talking analogizing SoCs as the sports-cars of the industry (fast but expensive), and FPGAs as the station wagons (not cool). In fact he even said that when Xilinx… Read More

Wally’s u2u keynote

I was at Wally’s u2u (Mentor user group) keynote yesterday. The other keynote was by Ivo Bolsens of Xilinx and is here. He started off by looking at how the semiconductor industry has recovered and silicon area shipments are now back on trend after a pronounced drop in 2009 and revenue has followed. Finally the semiconductor… Read More

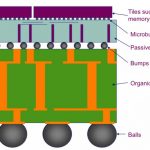

The World’s Smallest Printed Circuit Boards: interposers

Have you ever had the experience where you look up some unusual word in the dictionary since you don’t remember seeing it before. And then, in the next few weeks you keep coming across it. Twice in the last week I have been in presentations about the economics of putting die onto silicon interposers and the possibility of a new… Read More

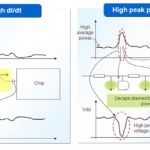

Semiconductor RTL Power Analysis: the sweet spot

Power has become the strongest driver of semiconductor design today, more important than area, more important than timing. Whether the device is handheld, like a wireless phone, or tethered, like a router, complex power and energy requirements must be met. Shrinking geometries continue to impose new challenges as power management… Read More

How Avnera uses Hardware Configuration Management with Virtuoso IC Tools

Introduction

Here in the Silicon Forest (Oregon) we have a venture-backed, fabless analog semi company called Avnera that has designed over 10 Analog System on Chips (ASoC). Their chips are used in consumer products for both wireless audio and video applications.

James Rollins is the director of physical design at Avnera… Read More

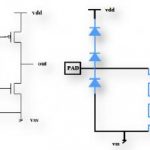

Transistor-Level Electrical Rule Checking

Introduction

Circuit designers work at the transistor level and strive to get the ultimate in performance, layout density or low power by creating crafty circuit topologies in both schematics and layout. Along with this quest comes the daunting task of verifying that all of your rules and best practices about reliability have… Read More

Thanks for the memory

One of the most demanding areas of layout design has always been memories. Whereas digital design often uses somewhat simplified design rules, memories have to be designed pushing every rule to the limit. Obviously even a tiny improvement in the size of a bit cell multiplies up into significant area savings when there are billions… Read More

What if China doesn’t want TSMC’s factories but wants to take them out?