It was a very late evening, perhaps 11 PM, on a warm summer night in 2008. Someone sent an email to info@cliosoft.com with a very odd question – why were we not listed in Wikipedia? The sender was a scientist working for the Lawrence Berkeley National Lab. Of course, this piqued my curiosity and I replied back asking why that concerns him so much? After a few email exchanges, I found out that his team was collaborating with scientists in several other research organizations in Europe to design the Atlas detector for the Large Hadron Collider in Switzerland. They were using the Cadence Virtuoso platform for analog mixed-signal design and looking for a design management solution to help collaborate and share design data efficiently. Of course, being a research organization, they had limited budgets. This seemed like an absolutely worthy project to be associated with and the Cliosoft Academic program was born! Here is a paper in EDN magazine with more information about this project.

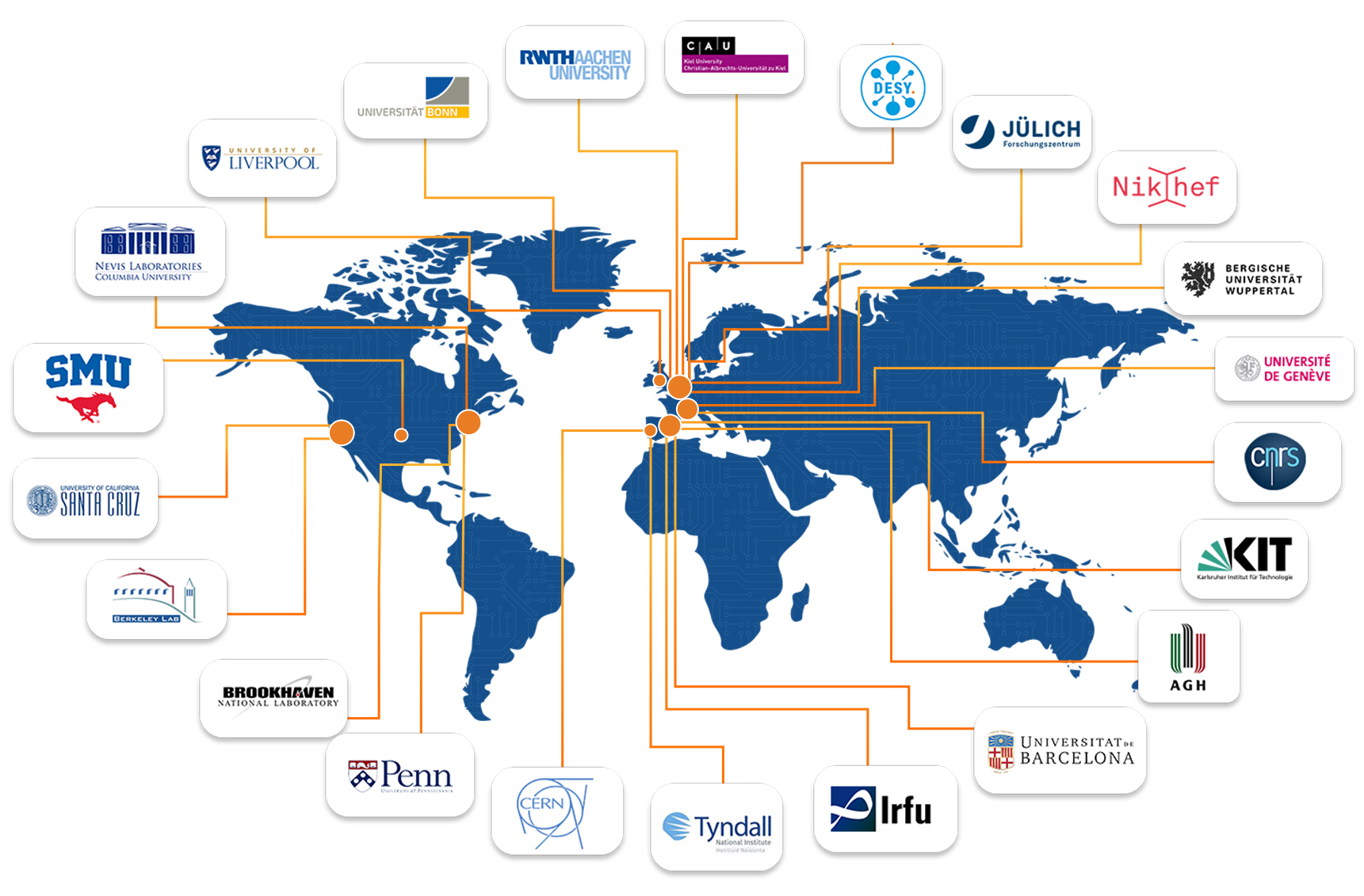

We were a small company and we really did not have the resources to promote and nurture an Academic program. However, purely through word of mouth, we got requests for academic licenses from Nikhef in the Netherlands and DESY and the RWTH Aachen University in Germany in 2009. In 2011, two of Europe’s premier research organizations, CERN in Switzerland and CNRS in France adopted the Cliosoft SOS platform. Academic requests started trickling in at a much faster rate, mostly from Europe, even though our Academic program wasn’t even mentioned on our website. Many of them were physics researchers collaborating with one or more of the research organizations using Cliosoft SOS.

Dr. John McLean, Head, Microelectronics Support Centre and Manager Europractice Design Tool Service, came to our DAC booth in 2016. We were surprised by this as our previous attempts to get listed with Europractice had, to be honest, fallen on deaf ears. Europractice supports only a select few EDA vendors and they did not have much interest in a design management vendor. John was blunt and honest with us. I am paraphrasing, but he said something along the lines of “We didn’t think that there was a big enough interest, but it appears that the Physics community in Europe has standardized on your solution”. The power of physics is how Cliosoft made it to the select list of EDA vendors supported by Europractice.

It took a little while for word to cross the pond but now we have research organizations and universities in North America using our design management solutions. These include research organizations such as Brookhaven Labs, Stanford SLAC, and Triumf, and universities such as Cornell, SMU, Pennsylvania, and UC Santa Cruz.

Since that summer night in 2008, this program has been a special child for me. I feel proud and honored that some of the best minds in the world actually use our software to explore the nature of the universe. While pottering around in COVID-19 isolation, I realized that we now have over 40 academic institutions using our software to help with their deep scientific research. I thought I would write this blog to celebrate that milestone. I reached out to several of the scientists to find out what type of work they are doing and how Cliosoft’s SOS has helped them. Listed below are quotes from some of the smartest people we have had the honor of working with.

If you are engaged in academic or research activities and would like to license our software through our academic program then contact us by emailing: edu@cliosoft.com

Wojciech Bialas

- Engineer/CAD Manager, Experimental Physics Department

- CERN – European Organization for Nuclear Research

Microelectronics section at CERN is principally involved in the design of a variety of ASICs related to four major LHC experiments of general purpose: ATLAS, CMS and specialized ones: ALICE, LHCb.

Starting to use Cliosoft suite of tools by our community was clearly a turning point for us. It came really at the right moment. We were in the middle of electronics design challenge for LHC experiments planned upgrades, where the complexity of ASICs foreseen went up by an order of magnitude from what we were doing before. Microelectronics engineers in the High Energy Physics (HEP) community were geographically and institutionally very much dispersed. Collaboration on these demanding projects in that conditions was really difficult. The Cliosoft SOS solution met perfectly our needs, introducing smooth data exchange between HEP community designers. It also brought us design exploration solutions. Inside our CERN microelectronics section we de facto made Cliosoft data management a standard. Considering all these benefits, nowadays all our projects are receiving SOS data management configuration by default. By using it we simply started to be more efficient in our work.

Maurice Garcia-Sciveres

- Senior scientist, Physics Division, Lawrence Berkeley National Laboratory

ASICs are an integral part of particle physics experiments and many PhD students are involved in IC design projects. However, particle physics experiments are also carried out by large collaborations of people from many institutions all over the world. The ATLAS.ch experiment, for example, has over 1000 PhD students from 180 institutions. People working on a particular ASIC design will generally not be co-located. Collaboration tools are essential to enable students to work on real ICs that will be used in the experiment. Over the past decade, Cliosoft’s SOS has become the standard tool for integrating particle physics ASICS, greatly enhancing student involvement.

Here are just a few of the projects I was involved in:

Luca Pacher, University of Torino, PhD 2015: “Development of Integrated Pixel Front-End Electronics in 65 nm CMOS Technology for Extreme Rate and Radiation at HL-LHC”, developed digital control and readout for high rate pixel detectors. Project was organized with Cliosoft leading to final submission in 2017.

Ennio Monteil, University of Torino, PhD 2017: “Front-end electronics in 65nm CMOS technology for the HL-LHC upgrade”, has been working on the design of an analog front-end in 65nm CMOS technology inside the CERN RD53 collaboration. This activity relied on Cliosoft for chip integration.

Sara Marconi, Perugia University, PhD 2018: “Design and optimization of low power hybrid pixel array logic for the extreme hit and trigger rates of the Large Hadron Collider upgrade”, designed digital elements and developed UVM verification framework for pixel readout circuit. Full design managed on Cliosoft.

Tomasz Hemperek, Bonn U. PhD 2018: “Exploration of advanced CMOS technologies for new pixel detector concepts in High Energy Physics”, Development of radiation hard monolithic pixel sensors that can replace hybrid pixel sensors in high energy physics experiments in various technologies (110-180nm). Most using Cliosoft.

Veronica Wallangen, U. of Stockholm PhD 2019: “Performance Improvements for Particle Tracking Detectors in Extreme Rate and Radiation Environments”. Designed a 65nm CMOS DFE circuit for 5Mbps NRZ transmission, which was included in a test chip assembled and submitted by collaborators at Southern Methodist University, via Cliosoft.

Cesar Gonzalez-Renteria, UC Berkeley PhD in progress: Worked on digital verification of 65nm CMOS pixel readout chip. Mostly RTL code, but relying on Cliosoft for chip integration.

Piotr Rymaszewski, Bonn U. PhD in progress: “Design and characterization of pixel IC electronics and sensors for a new pixel detector generations”, Development of radiation hard IP in 65nm inside the CERN RD53 collaboration and radiation hard monolithic pixel sensor in 150nm technology for ATLAS like environment (LF-Monpix series). Both using Cliosoft.

Kostas Moustakas, Bonn U. PhD in progress: “Development of Depleted Monolithic Active Pixel Sensors with Small Collection Electrode for LHC”, Development of radiation hard IP in 65nm inside the CERN RD53 collaboration and radiation hard monolithic pixel sensor in 180nm technology for ATLAS like environment (TJ-Monopix series). Both using Cliosoft.

Nick Van Helleputte

- R&D Manager, Biomedical circuits and system, imec

Our team focuses on analog-mixed-signal ASIC design for ultra-low-power biomedical applications. As our team has grown, so did the complexity of our ASIC designs. While initially our research focused on analog readout circuits for various biomedical parameters, we gradually moved towards highly integrated true SoCs with analog readouts, analog-to-digital converters, digital signal processing, power management and wireless communication capabilities all in single-chip solutions. This eventually meant larger design teams and multiple collaborators, sometimes spread across different countries. It became clear that to ensure successful and efficient design, we needed a suitable design management tool.

We opted for Cliosoft SoS and never regretted this decision. Version control is an integral part of a decent quality assurance design flow and is extremely well implemented in SOS. In addition, it allows efficient collaboration across multiple teams. Roll-back to previous versions and design IP re-use are features we have come to rely upon on a daily basis.

However, Cliosoft SOS did not only prove to be valuable for these large ambitious projects. After seeing the benefits SOS offered in our larger research projects, while still being easy to set up and intuitive to use, we decided to make it part of our standard design flow for all design projects. Roughly half of our ASIC designs are PhD researchers who are often working on a research topic by themselves or in a smaller group of 2 to 3 designers. They are now also using Cliosoft SOS. This has proven extremely efficient as our PhD researchers can now more efficiently share common design libraries and it has become much easier to involve extra resources close to tape-outs to help the students out when needed. And last but not least, the hard research effort is so much easier to integrate into our various research programs after the PhD finishes.

Barend Van Liempd

- Program Manager Radar ICs, imec

At Imec’s IoT department, all our circuit design projects (focus on high-capacity wireless network circuits and radar chip designs) in a variety of technology nodes are maintained on Cliosoft SOS. We started using it in year 2016 and it has been a satisfying experience so far.

Before the use of Cliosoft, designers had a number of “best practices”, including local libraries and include all the libraries in the cds.lib. With Cliosoft SOS in place, we have optimized and improved on this workflow, and thus have increased productivity.

The number of Cadence libraries are reduced considerably and so is the library management. It also resulted in better collaboration among the team, as everyone is working on a limited number of Cadence libraries. The managed libraries helped multiple users to work on the same cell.

The Cliosoft SOS integration with Cadence Virtuoso is smooth. The customer support has been excellent. The technical staff was able to resolve our issues/concerns on time.

Coronavirus crisis effect on tapeouts?

Since the design work-flow was version controlled, the coronavirus crisis did not adversely affect our work-flow and we had successful tape-outs according to planned milestones.

Patrick Pangaud

- Responsable du Service Electronique – Head of the Department of Electronics

- CENTRE DE PHYSIQUE DES PARTICULES DE MARSEILLE

- UMR 7346 – Aix-Marseille Université – CNRS/IN2P3

For more than 10 years, the laboratories of IN2P3 (https://in2p3.cnrs.fr/en) (a CNRS institute) have been using CLIOSOFT tools for their realizations dedicated to physics experiments. IN2P3 develops its research programs in Astroparticles, Particle Physics, Nuclear Physics through 25 laboratories and platforms with a staff of 2500 researchers and engineers. The first project started in 2008, with the contribution of CPPM (one IN2P3 laboratory) to the effort on the FE-I4 project. This readout chip was made for the upgrade of the pixel detector of the CERN ATLAS particle physics experiment, led by the LBNL with implications of CPPM, Bonn University, NiKHEF, Genova University. The SOS tool was the solution to share and build blocks all together all over the world. After this successful realisation, IN2P3 decided to get tokens for all its laboratories.

IN2P3 applications are designed by 14 teams spread all over France in a microelectronics cluster with a unified management: regular internal meetings, training program and school, sharing knowhow, common CAD tools, sharing technologies and IP exchanges…

Using Cliosoft SOS design management allows us to build very large teams with specific expertise coming from laboratories all over the world. Indeed, our engineers participate with other relevant teams from LBNL, Fermilab, CERN, Bonn University, the Italian INFN laboratories, Nikhef, CEA-IRFU and even more for the upgrade of the next physics experiments with an important contribution to the Large Hadron Collider (LHC) detectors’ upgrades, based in CERN, Geneva. We can quote in recent years the RD53 project for the ATLAS and CMS inner detectors’ upgrade, or the HGCROC for the CMS High Granularity Calorimeter, among others.

Engineers also contribute to Societal Applications: Beam profiler for radiation therapy, medical imaging, Compton camera, dosimetry…and they participate to international R&D and academic programs like CERN’s initiatives for R&D on Experimental Technologies as RD50 (Radiation hard semiconductor devices for very high luminosity colliders, 2018) and RD53 (Development of pixel readout integrated circuits for extreme rate and radiation, 2013), European Framework program H2020 : ATTRACT (2018) and AIDA (2011) or 3D-IC (three-dimensional integrated circuit, 2009).

Roberto Beccherle

- Technology Researcher, INFN – Istituto Nazionale di Fisica Nucleare

We work for an upgraded version of the Pixel Detector readout ASIC, for ATLAS and CMS experiments at the LHC at CERN, within the RD53 collaboration.Being an academia research team, our design team is split across many countries both in US (LBNL) and Europe (Bonn, Marseille, Paris, Pisa, Bari, Torino, Bergamo/Pavia), and assembling such a complex design, in our distributed working environment would have been literally impossible without daily usage of Cliosoft’s SOS seamless integration features that allow remote designers to effectively work and collaborate on a distributed chip development.

Ruud Kluit

- Group leader Electronics Technology, Nikhef

Nikhef is the Dutch National Institute for Sub-atomic particle physics, and in this field of physics, Nikhef does fundamental research on known and yet unknown (predicted) particles. For this, instrumentation, like particle accelerators, and detectors are needed, and these are the technical systems Nikhef engineers, technicians and scientists work on. Since the detectors are often in a radiation environment, the electronics, and also sensors (detectors) with their readout IC’s, need to be able to operate under irradiation. This requires specific expertise, and this is spread over the world wide sub-atomic physics community in which we operate. So, in order to develop the ASIN’s, we always need a collaboration of engineers, and so a smooth exchangeability of design- parts and files is required to develop the ASIC’s efficiently together. In one of such a collaboration, Nikhef (Netherlands) together with Berkeley National Laboratories (US), the university of Bonn (Germany) and Marseille (France), we started exploring the Cliosoft tools in May of 2008. In the years after we experienced the power of such a tool and the ease to interactively exchange design parts, which we experienced to be very efficient for the design process. Later on, SOS (name of the tool), was used in more projects, where several engineers work on one ASIC, collaboration became increasingly important due to the increasing complexity of the ASIC’s and tools. But even in the case where a single engineer does the design, the use of version management is very efficient. Another advantage is the easy synchronisation of the latest PDK versions and tool options for the designers in a team.

David Gascón Fora

- Associate Professor, University of Barcelona

- Director of the Technology Unit of the Institute of Cosmos Science of the UB (ICCUB)

- http://icc.ub.edu/technology/unit.

ICCUB is focused on the development of scientific instrumentation for High Energy Physics and Astrophysics, among other fields. We have been developing the front end electronics for the calorimeter and scintillating fiber tracker detectors. This involves the design of radiation-tolerant Application-Specific Integrated Circuits (ASICs) for the LHCb experiment at CERN (https://lhcb-public.web.cern.ch/). The ICCUB-TECH has also designed ASICs for some of the cameras of the Cherenkov Telescope Array Observatory (https://www.cta-observatory.org/): a preamplifier (PACTA), two amplifiers (ACTA/MUSIC) and a trigger unit (L0).

We work in highly cooperative projects. Hence we use Cliosoft’s SOS solution, both internally, as the design management system for ASIC design, and also to collaborate with our colleagues at CERN and other European institutes. A design management tool like SOS is mandatory in collaborative projects. Moreover, the fact that SOS is integrated into the native library manager is extremely helpful.

Paul Hyland

- Operations Manager, MCCI – Microelectronic Circuits Centre Ireland, Tyndall National Institute

Microelectronic Circuits Centre Ireland is in the “business” of academic research. We want to enable our researchers to do world-class research and publish at top conferences. This helps their careers and excites the industry partners that follow and support our research programs. Our research is focused on analog mixed-signal and RF chip design. We rely on Cliosoft SOS to manage our Cadence design databases and to facilitate easy collaboration between multiple researchers. The version management capabilities within Cliosoft are essential for such an iterative design process as we often need to step back to older versions. We use Cliosoft to tag project databases to clearly identify different design milestones and especially what we taped out. We also have a strong desire to have our researchers use industry-standard tools such that they will be more valuable hires to industry.

Johan Bauwelinck

- Professor at IDLab, Ghent University, in collaboration with IMEC

Our users are about 50/50 PhD students/postdoctoral researchers, all in Gent. We use the SOS design management software for managing our high-speed transceiver IC designs. The tool allows versioning not only the Cadence libraries but also Keysight ADS design files. Rolling back to a previous version is easy, and we can clearly communicate file status using tags. Moreover, this software facilitates collaborating on large projects.

Richard Leys

- Research Associate, Karlsruhe Institute of Technology (KIT)

The ASIC and Detector Lab Group at KIT was created in 2014 by Prof. Peric, and counts roughly 10 users between Scientists, PhDs and Students.

When setting up at KIT, we had to build our small infrastructure from scratch and moved straight to using SOS for data exchange. It greatly facilitated setting up the repositories, backups and collaboration across all user scenarios. The ability to quickly check file status on large design databases greatly eases collaborative work, even more in a time where remote office has suddenly developed to a new standard.

As members of the large High Energy Physics and Astrophysics experiments landscape, we regularly share designs with partner institutions, which is highly facilitated by the widespread adoption of SOS.

Clive Holmes

- Deputy Head, Europractice Design Tool Service, STFC Rutherford Appleton Laboratory

Europractice provides services to the European academic sector to enable them to more easily use leading microelectronics technologies and adopt advanced design methodologies in their teaching and research. Cliosoft’s SOS integrates well and complements the existing design tools within the Europractice portfolio and better facilitates work on large, often collaborative, projects within the academic sector.

As seen on https://www.cliosoft.com/resources/blog/

Also Read

A tour of Cliosoft’s participation at DAC 2020 with Simon Rance

How to Grow with Poise and Grace, a Tale of Scalability from ClioSoft

How to Modify, Release and Update IP in 30 Minutes or Less

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.