Apple’s recent bout with ‘Batterygate’ highlighted just how important dynamic power management can be. Our last Sonics update looked at using their NoC to manage power islands; this time, we look at their research progress on architectural measures for power management.… Read More

How to handle petabyte-scale traffic growth?

If you search the web for IP traffic growth, you will find many graphics, but the common result is that IP traffic is growing with high CAGR for many years and will again continue to grow with such high CAGR for the next five years. For example the global mobile data traffic is expected to grow with 53% CAGR 2015-2020… even if the smartphone… Read More

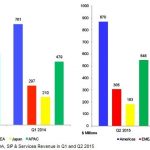

Positive pointers from Samsung, GF, Renesas, NXP/Freescale, ST, Soitec – so will 2016 be the year of FD-SOI?

A little over a month into 2016 and we already have a raft of FD-SOI news from Samsung, GlobalFoundries, NXP/Freescale, Renesas and more. Quite a bit of it came out of the recent SOI Consortium forum in Tokyo. Many of the presentations are now available on the SOI Consortium website (click here to see what’s there) – but keep checking… Read More

IP Vendor Nabs Top Talent from Semiconductor Industry

The growth of mobile and IoT have helped increase the demand for One Time Programmable Non Volatile Memory (OTP NVM) as a solution for on-chip storage. To continue to meet this demand and grow with it, industry leading Sidense has recently brought on board seasoned semiconductor executive Ken Wagner as VP of Engineering. He was … Read More

Submerging the Data Center

One of NetSpeed’s customers is a Tier-1 semiconductor company that develops some of the industry’s best performing and most complex system on chips (SoC) for the data center and cloud computing markets. To keep its leadership in the data center market, the company needs to produce best-in-class SoC solutions year after year. … Read More

In Low Voltage Timing, the Center Cannot Hold

When I started discussing this topic with Isadore Katz, I was struggling to find a simple way to explain what he was telling me – that delay and variance calculations in STA tools are wrong at low voltage because the average (the center) of a timing distribution shifts from where you think it is going to be. He told me that I’m not alone… Read More

Coventor ASML IMEC: The last half nanometer

On Tuesday evening December 8[SUP]th[/SUP] at IEDM, Coventor held a panel discussion entitled the “The last half nanometer”. Coventor is a leading provider of simulation software used to design processes. This is my third year attending the Coventor panel discussion at IEDM and they are always excellent with very strong panels… Read More

How to Build a Deadlock-Free Multi-cores SoC?

We will precisely explain the meaning of deadlock in a modern, complex multi-core SoC. First, let’s take a look at the crash of the Air France 296, when a brand new Airbus A320 crashed during a demo flight on June 26, 1988. This Airbus 320, the first plane being completely automated, thanks to the FADEC flight system, was running a demo… Read More

IP Development in Japan

As semiconductor IP is growing bigger in size and more complex in providing complete solution for a particular functionality in an SoC, regions from across the world are joining to provide various types of services in the overall value-chain of IP development, verification, and its integration into SoCs. … Read More

Networking through Dark Silicon Power Islands

For decades, tracing back to the days of Deming, the way to tackle complex engineering problems has been the pareto chart. Charting conditions and their contribution to the problem leads to mitigation priorities.

In the case of SoC power management, the old school pareto chart said the processor core was the biggest power hog and… Read More