Bram co-founded ICsense in 2004 as a spin-off of the University of Leuven. He is CEO since 2004 and helped growing the company from 4 to over 100 people in 20 years while being profitable every year. He managed the acquisition by TDK in 2017. He is an experienced entrepreneur in the micro-electronics field with a strong interest in efficiently managing design teams and delivering projects with high quality.

Bram is a board member of Flanders Semiconductor, a non-profit organization that represents the Belgian semiconductor ecosystem. He is also member of the Crown Counsel of SOKwadraat, a non-profit organization to boost the number of spin-offs in Belgium. He holds a MSc. degree in micro- electronics and a Ph.D. from the Katholieke Universiteit Leuven, Belgium. Bram has been a research and postdoctoral assistant with ESAT-MICAS laboratories with Prof. M. Steyaert.

Tell us about your company?

At ICsense, we specialize in analog, mixed-signal and digital ASIC (Application-Specific Integrated Circuit) developments. We handle the complete chain from architectural definition, design, in-house test development upto mass production of the custom components. Today, we are one of the largest fabless European companies active in this domain.

I co-founded ICsense with 3 of my PhD colleagues back in 2004. Our focus has always been on analog, digital, mixed-signal, and high-voltage ICs, serving diverse industries including automotive, medical, industrial, and consumer electronics. ICsense is headquartered in Leuven, Belgium and has a design center in Ghent, Belgium. The semiconductor ecosystem in Belgium is quite lively, with imec as a renown research center, world class universities and many industrial players in different parts of the semiconductor value chain represented by Flanders Semiconductors.

In 2017, we became part of the Japanese TDK Group (www.tdk.com), a leading supplier of electronic components. This enabled us to continue our strategy and serve customers worldwide as before. What many people don’t realize is that the majority of ICsense’s business today is outside the TDK Group!

Joining TDK has allowed us to grow faster and broaden our activities. We have invested in ATE (Automated Test Equipment, mass production testers and wafer probers) to do test program developments in-house. This makes ICsense unique in the market of ASIC suppliers, capable of building some of the highest-performance ASICs and bringing them into production for our customers.

What problems are you solving?

Many industries require specialized ICs tailored to specific applications, that off-the-shelf solutions often cannot adequately serve. To meet this need, we design custom ASICs for automotive, medical, industrial, and consumer electronics sectors, ensuring optimal performance and functionality.

Designing high-performance analog and mixed-signal ICs is inherently complex and requires specialized expertise. This expertise is the reason our customers knock on our door. Leveraging our extensive experience in analog, digital, mixed-signal, and high-voltage ICs, we deliver robust and reliable solutions. We develop advanced sensor interfaces, power management solutions, high-voltage actuation and sensing circuits, ultra-low-power circuitry and communication chips.

Every chip is uniquely build for one single customer at a time and only supplied to that customer. The customer’s IP is fully protected to keep his competitive edge in the market.

What application areas are your strongest?

In our 20 years of existence, we have built up a strong track record in complex ASIC developments in different technology nodes and for many different applications. We often push the boundaries to reach the highest performance or tweak the last uA out of a circuit. We are definitely not an “IP-gluer” (i.e. a company that simply combines existing IP blocks without modifications). Our design work is mostly custom, to meet the challenging requirements our customers are faced with.

Over the past 10 years, we have seen a strong growth in industries such as automotive and medical that require ICs meeting stringent quality and reliability standards. To address this, we employ rigorous design techniques. ICsense works according ISO13485 (medical) and ISO262626 (automotive) compliance standards. To give you one example, all the automotive ASICs we developed in the last 5 years are at least ASIL-B(D) Functional Safety level.

What keeps your customers up at night?

It really depends on the specific customer. We don’t have a typical client profile; our customers range from startups to large multinationals, from semiconductor companies to OEMs, each with their own unique concerns and expectations. In the medical market, for example, we collaborate with industry leaders in implants, such as Cochlear, as well as with brand-new startups aiming to bring novel ideas to new markets. The common ground among all our clients is their need for a partner who can build innovative, state-of-the-art ASICs with low risk and who supports sustainable production. They appreciate that ICsense combines the flexibility and dynamic team of a startup company, with the rigour, stability and sustainability of a large company.

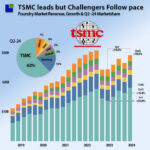

In recent years, another major concern for our customers has been de-risking their supply chains. Discussions now frequently revolve around second sourcing and geopolitical issues. In response, we have been exploring more technology and partner options across the supply chain. Today, we are one of the few companies worldwide that can offer IC design in over 50 technology flavors, with fabrication facilities in the US, Europe, and Taiwan. Our specific design methodology allows us to efficiently work across various technology nodes, ensuring we can select the best match for our customers.

What does the competitive landscape look like and how do you differentiate?

Lately, there has been a lot of consolidation in the semiconductor value chain in Europe. As a result, ICsense remains one of the few companies of its size and capabilities that can serve external customers. Thanks to our mother company TDK, we can provide ASICs to Fortune 500 companies and to smaller companies and startups at the same time. With a team of over 100 skilled designers and in-house ATE and product engineering, we have a unique position in ASIC design and supply to the medical, industrial, consumer and automotive markets.

What new features/technology are you working on?

All our ASIC developments are customer specific. Some will hit the market as ASSP by our customer, most as part of a single product. Therefore, all the technology and features we are developing are confidential. We see some trends in the market, such as a shift towards smaller technology nodes (although not deep submicron) and a shift towards more differentiation in supply chain. Our technology-agnostic design approach is quite powerful to capture this trend.

Another trend is the push to higher integration and more functionality in many applications, from medical implants to industrial devices, that push the boundaries of the state-of-the-art. Again, this is one of our core strengths.

How do customers normally engage with your company?

We work with customers in 2 models: the first is a pure design support model, where we act as a virtual team to our customer. We perform the full design and hand over the design files, so our customer can integrate this further or handle the manufacturing themselves. Our second and most popular model is the turnkey supply model or -as we call it- ASIC design and supply. We handle the complete development from study upto mass production for our customer and we supply the ASICs to them throughout the lifetime of their product.

An ASIC design can start with just a back of the envelope idea or a full product requirement. Whatever the starting point, our first step is always to do a feasibility and architectural study in which we pin down all the details of the design to be made, define boundary conditions and prove with calculations and preliminary simulations that the requirements can be met.

We then proceed to the actual implementation, the design and layout work, which is the bulk of the work in the project. Through the design cycle, we continuously perform in-depth verification from transistor to chip top level to make sure all use cases are covered prior to the actual manufacturing of the wafers. In parallel to the manufacturing of the engineering silicon, we develop the ATE test hardware and software so that when the silicon returns from the fab, we can immediately start testing.

We have a good track record in first time functional designs, meaning that the ASIC is fully functional and can be used to build prototypes at the customer side. We typically only need a respin to fix small items and to optimise the yield. This is a result of our proprietary, systematic design flow based on commercially available EDA tools such as Cadence, Synopsys and Siemens.

The last stage is industrialisation, including qualification of the chips and perform additional statistical analysis to prove robustness over the lifetime of the product. Our product engineering team supports our customer with the ramp up, start of production and monitoring of yield, … during production. The supply model, direct or through partners, depends on the volume and the type of customer.

Also Read:

CEO Interview: Anders Storm of Sivers Semiconductors

![IMG 0411[6]](https://semiwiki.com/wp-content/uploads/2024/08/IMG_04116-150x100.jpg)