Imagine being able to use any combination of EDA vendor tools for schematic capture, SPICE circuit simulation, layout editing, place & route, DRC, LVS and extraction. On the foundry side, how about creating just a single Process Development Kit (PDK), instead of vendor-specific kits. Well, this is the basic premise of a recent… Read More

Tag: webinar

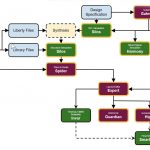

IC Design and OpenAccess

EDA vendors have long used proprietary file and database formats to keep their users locked into their specific tool flow and keep any competitors from sharing in the IC design process. Along the way the actual users of EDA tools have often requested and helped to create interoperable flows so that they could mix and match multiple… Read More

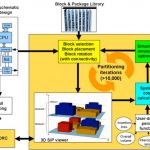

Learning about 3D Integration of ICs and Systems

We blog a lot about Moore’s Law, and even “More than Moore” where 3D integration of ICs and systems are used to get lower product costs. One big challenge with 3D integration of ICs is that most EDA software was really intended only for abstracting at 2D or 2.5D structures. Over the past several years there have … Read More

Design For Safety in Automotive Electronics

Do you remember how auto maker Toyota had to pay a $1.2 billion settlement in 2014 because some of their automotive models experienced sudden, unintended acceleration? That scenario has to be an engineer’s worst nightmare because something was missed during the design and testing of an automotive electronics system that… Read More

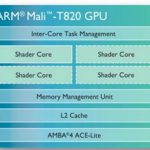

How ARM Implemented a Mali GPU using Logic Synthesis and Place/Route Tools

ARM is a well-known semiconductor IP provider and they often create a reference design so that SoC companies can have a starting point to work with. On the GPU side of IP the ARM engineers have an architecture called Mali, and a recent webinar hosted by Synopsys reviewed how the physical design area was minimized by using a combination… Read More

Tackling Layout Gradient Effects in 16 nm FinFET using Layout Automation

My first exposure to automating IC layout was back in the 1980’s at Intel where I coded a layout compiler to auto-generate about 6% of a graphics processor chip. The need to use automation for IC layout continues today, and with the advent of FinFET technology there are some new challenges like layout gradient effects that … Read More

How Sidense Sees The Smart Connected Universe

Sidenserecently conducted a webinar on what they call the Smart Connected Universe. They consider the Smart Connected Universe as something that includes a collection of market segments that are both smart and connected. This casts a big net, and includes what many are calling IoT, but goes further into medical, automotive and… Read More

Webinar: Choosing IP for your next IoT Design

My favorite IoT device is a cycle-computer from CatEyeand it has GPS for tracking my bike routes, and an LCD display that shows me speed, cadence, heart rate and time. After each ride I connect my CatEye device to a USB connector, upload my data to Strava.com, and then see how I’m doing versus other cyclists and my own personal… Read More

Using NoCs to Reduce Power

Earlier this week I moderated a webinar at Sonics entitled NoC 102: Using SonicsGN to Address Low Power Requirements. Drew Wingard, the CTO of Sonics, presented it. It goes without saying that power is a major concern in SoC design, not just with chips for battery powered devices but also tethered devices. A major cost of ownership… Read More

NoC 102: Using SonicsGN to Address Low Power Requirements From IoT to Servers

At the end of last year, I moderated a Sonics webinar to introduce the concept of a network-on-chip or NoC. It was called NoC 101 and the replay is still available here.

Well it is a new year and time for chapter 2. I will be moderating a webinar next Wednesday February 4th at 10am pacific time. Once again the webinar itself will be delivered… Read More