The performance demands of data centers continue to grow, driven to large degree by the ubiquitous use of complex AI algorithms. On April 25, Embedded Computing Design held an informative webinar on this topic. Two experts looked at the problem from the standpoint of processor architecture and communication strategies, which… Read More

Tag: CXL

CEO Interview: Sanjeev Kumar – Co-Founder & Mentor of Logic Fruit Technologies

Sanjeev is a renowned technopreneur in the semiconductor industry. With more than 20+ years of experience, he is known for his enormous resilience and deep tech knowledge that sets him apart from others in the industry.

Sanjeev started his career as a hardware designer and then forayed into the FPGA domain due to his love for configurable… Read More

Why Secure Ethernet Connections?

While web browsing I constantly glance for the padlock symbol to indicate that the site is encrypting any of my form data by using the https prefix, which means that an SSL (Secure Sockets Layer) certificate is being used by the web hosting company. I have peace of mind knowing that my credit card information cannot be easily stolen… Read More

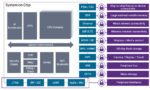

Chiplet Interconnect Challenges and Standards

For decades now I’ve watched the incredible growth of SoCs in terms of die size, transistor count, frequency and complexity. Instead of placing all of the system complexity into a single, monolithic chip, there are now compelling reasons to use a multi-chip approach, like when the maximum die size limit is reached, or it’s… Read More

Optimization Tradeoffs in Power and Latency for PCIe/CXL in Datacenters

PCI Express Power Bottleneck

Madhumita Sanyal, Sr. Technical Product Manager, and Gary Ruggles, Sr. Product Manager, discussed the tradeoffs between power and latency in PCIe/CXL data centers during a live SemiWiki webinar on January 26, 2023. The demands on PCIe continue to grow with the integration of multiple components… Read More

How to Efficiently and Effectively Secure SoC Interfaces for Data Protection

Before the advent of the digitized society and computer chips, things that needed protection were mostly hard assets such as jewelry, coins, real estate, etc. Administering security was simple and depended on strong guards who provided security through physical means. Then came the safety box services offered by financial … Read More

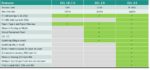

Verification IP Hastens the Design of CXL 3.0

Although version 2.0 of the Computer Express Link (CXL) standard is just making it into new designs, the next generation, version 3.0, has been approved and is now ready for designers to implement the new silicon and firmware needed to meet the new standard’s performance specifications. CXL, an open industry-standard interconnect,… Read More

Truechip: Customer Shipment of CXL3 VIP and CXL Switch Model

The tremendous amount of data generated by AI/ML driven applications and other hyperscale computing applications have forced the age old server architecture to change. The new architecture is driven by the resource disaggregation paradigm, wherein memory and storage are decoupled from the host CPU and managed independently… Read More

Interface IP in 2021: $1.3B, 22% growth and $3B in 2026

If you want to remember the key points for Interface IP in 2021, just consider $1.3B, 22%, $3B. Interface IP category has generated $1 billion 300 million in 2021, or 22.7% year to year growth, thanks to high runner protocols PCIe, DDR memory controller and Ethernet/SerDes. Even more impressive is the forecast, as IPnest predict… Read More

CXL Verification. A Siemens EDA Perspective

Amid the alphabet soup of inter-die/chip coherent access protocols, CXL is gaining a lot of traction. Originally proposed by Intel for cross-board and cross-backplane connectivity to accelerators of various types (GPU, AI, warm storage, etc.), a who’s who of systems and chip companies now sits on the board, joined by an equally… Read More