With time-to-market pressures ever increasing, companies are continually seeking enhanced designer productivity, faster design closure and improved project management efficiency. To accomplish these, organizations invest a lot in implementing both standardized approaches and proprietary techniques. With ever increasing… Read More

Tag: analytics

ISC 2022

SC 2022 – #TRANSFORMINGTHEFUTURE

THE EVENT FOR HIGH PERFORMANCE COMPUTING, MACHINE LEARNING AND DATA ANALYTICS

ISC HIGH PERFORMANCE 2022 PROGRAM

ISC High Performance is focused on bringing the most critical developments and trends in HPC, machine learning, and high performance data analytics to conference attendees.… Read More

Optimizing SoC performance in-life with Embedded Analytics

In many aspects of our lives, increasingly intelligent subsystems will do the thinking for us. 5G networks will self-tune to maximize their data throughput. Automation, with the help of AI, robotics, and the internet of things, is playing an increasing role in manufacturing. Vehicles are becoming ever more intelligent and autonomous.

Gartner Data & Analytics Summit

May 4 – 6, 2021 | Americas | Virtual

Optimization and verification wins in IoT designs

Designers tend to put tons of energy into pre-silicon verification of SoCs, with millions of dollars on the line if a piece of silicon fails due to a design flaw. Are programmable logic designers, particularly those working with an SoC such as the Xilinx Zynq, flirting with danger by not putting enough effort into verification?… Read More

Lethal data injection a much bigger threat

Watching a spirited debate on Twitter this morning between Tom Peters and some of his followers reminded me of the plot of many spy movies: silently killing an opponent with a lethal injection of some exotic, undetectable poison. We are building in enormous risks in more and more big data systems.… Read More

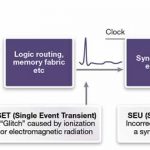

TMR approaches should vary by FPGA type

We’ve introduced the concepts behind triple modular redundancy (TMR) before, using built-in capability in Synopsys Synplify Premier to synthesize TMR circuitry into FPGAs automatically. A recent white paper authored by Angela Sutton revisits the subject… Read More

Should there be a 5-second IoT chip rule?

Kids have a tendency to put things in their mouths. Any parent can relate to the statement, “Put that down! You don’t know where it’s been!” After the first child, concern usually relaxes quite a bit. People joke about a 5-second rule on the premise if an object was just dropped on the floor, it may not be contaminated yet.… Read More

A moment of IoT silence before we disrupt

As I sat down in the SEMI Arizona Chapter breakfast meeting a few weeks ago, a moment of semiconductor history flew right before my eyes before the IoT sessions started.

We were seated in the cafeteria of Freescale Building 94 on Elliot Road in Tempe, a place I’d been many times before, except this time may have been the last. NXP is consolidating… Read More

Pushing on AXI-connected IP in FPGAs

Success stories are great. Reading how someone uses a product contributes much more insight than reading about a product. Last month we had a teaser for a presentation by Wave Semiconductor; this month, we have the slides showing how they are using FPGA-based prototyping, AXI transactions, and DPI to speed up development.

First,… Read More