Intro

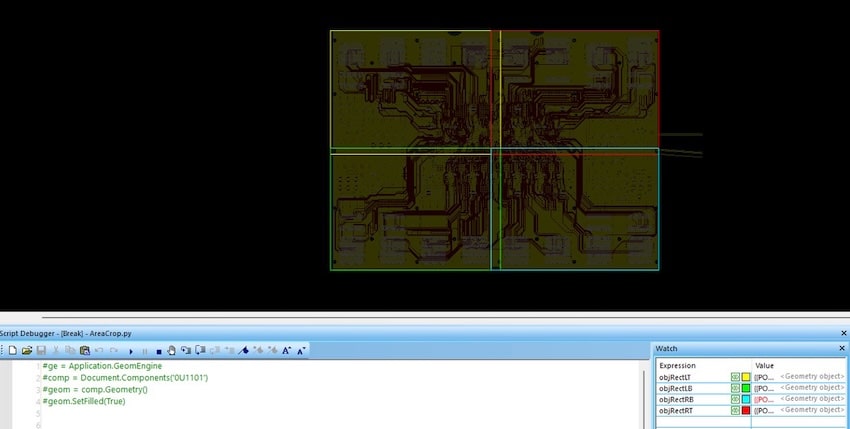

Micro Magic was the only company at DAC that showed an IC layout editor with 1 Trillion transistors loaded in it, wow.

Karen Mangum

Notes

I chatted with Katherine Hays, a 12 year veteran of Micro Magic about what was new at DAC this year.

Max-3D – Can handle stacked wafers with TSV

– Gary Smith’s list of must-see for 3D

–… Read More

If you believe in Hobbits you can believe in Rapidus