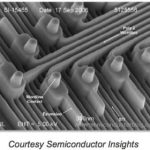

One of the most demanding areas of layout design has always been memories. Whereas digital design often uses somewhat simplified design rules, memories have to be designed pushing every rule to the limit. Obviously even a tiny improvement in the size of a bit cell multiplies up into significant area savings when there are billions… Read More

Semidynamics: A Single-Software-Stack, Configurable and Customizable RISC-V SolutionFounded with a vision to create transformative, customizable…Read More

Semidynamics: A Single-Software-Stack, Configurable and Customizable RISC-V SolutionFounded with a vision to create transformative, customizable…Read More Synopsys-Ansys 2.5D/3D Multi-Die Design Update: Learning from the Early AdoptersThe demand for high-performance computing (HPC), data centers,…Read More

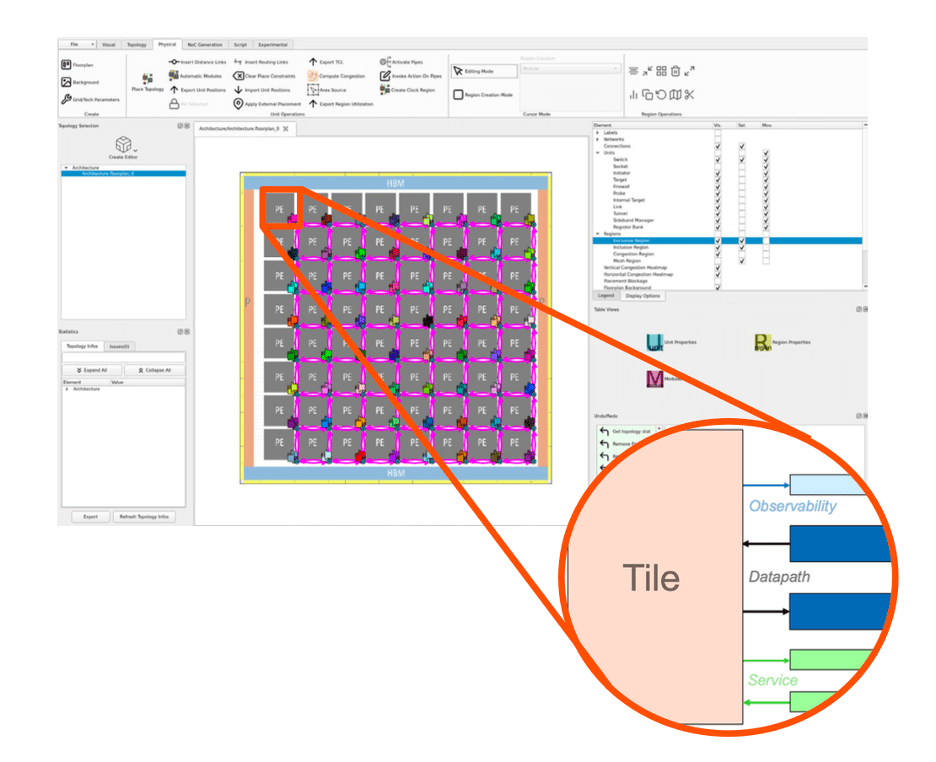

Synopsys-Ansys 2.5D/3D Multi-Die Design Update: Learning from the Early AdoptersThe demand for high-performance computing (HPC), data centers,…Read More Arteris Empowering Advances in Inference AcceleratorsSystolic arrays, with their ability to highly parallelize…Read More

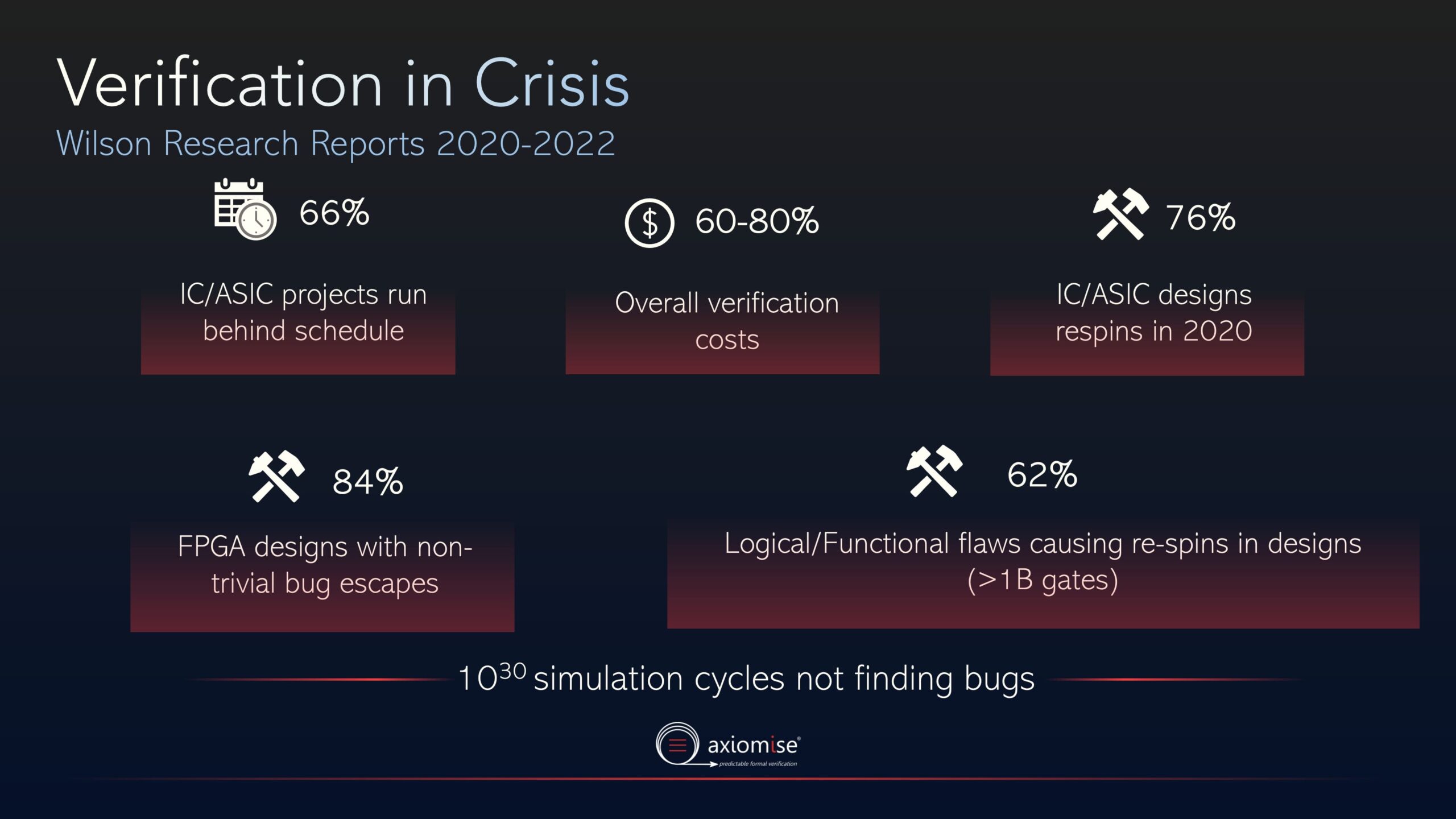

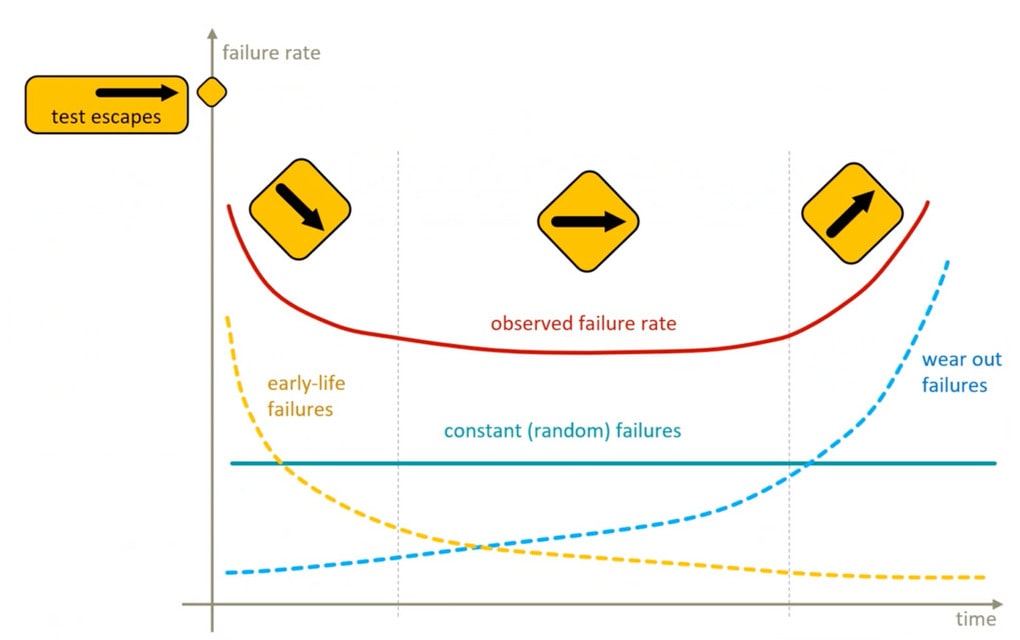

Arteris Empowering Advances in Inference AcceleratorsSystolic arrays, with their ability to highly parallelize…Read More The Convergence of Functional with Safety, Security and PPA VerificationFormal For All! “Do I need a PhD…Read More

The Convergence of Functional with Safety, Security and PPA VerificationFormal For All! “Do I need a PhD…Read MoreIntel Buys an ARMy. Maybe

Is Intel in trouble? Since it is the #1 semiconductor company and, shipping 22nm in Q4 this year with 14nm in 2013, it is two process generations ahead of everyone else it is hard to see why it would be. Intel, of course, continues to dominate the market for chips for notebooks, desktops and servers. But therein lies the problem. Pads… Read More

Semiconductor Virtual Platform Models

Virtual platforms have been an area that has some powerful value propositions for both architectural analysis and for software development. But the fundamental weakness has been the modeling problem. People want fast and accurate models but this turns out to be a choice.

The first issue is that there is an unavoidable tradeoff… Read More

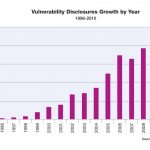

Semiconductor Industry Security Threat!

The IBM X-ForceTrend and Risk Report reveals how 2010 was a pivotal year for internet security as networks faced increasingly sophisticated attacks from malicious sources around the world. The X-Force reportedly monitors 13 billion real-time security events every day (150,000 events per second) and has seen an increase in … Read More

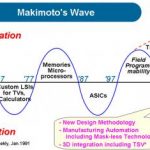

2011: A Semiconductor Odyssey!

Stanley Kubrick’s 2001: A Space Odyssey showed us a world where machine vision allowed a computer to watch and interact with its human colleagues. Yet after 40 years of incredible progress in semiconductor design, the technology to make computer-based image and video analysis a reality is still not practical.

While working with… Read More

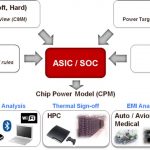

Chip-Package-System (CPS) Co-design

I can still remember the time, back in the mid-1980s, when I was at VLSI and we first discovered that we were going to have to worry about package pin inductance. Up until then we had been able to get away with a very simplistic model of the world since the clock rates weren’t high enough to need to worry about the package and PCB as… Read More

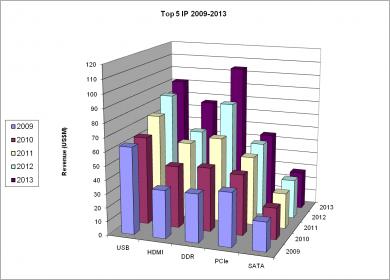

DDR4 Controller IP, Cadence IP strategy… and Synopsys

I will share with you some strategic information released by Cadence last week about their IP strategy, more specifically about the launch of the DDR4 Controller IP. And try to understand Cadence strategy about Interface IP in general (USB, PCIe, SATA, DDRn, HDMI, MIPI…) and how Cadence is positioned in respect with their closest… Read More

AMD and GlobalFoundries / TI and UMC

There have been some significant foundry announcements recently that if collated will give you a glimpse into the future of the semiconductor industry. So let me do that for you here.

First the candid EETimes article about TI dumping Samsung as a foundry:

Taiwan’s UMC will take the ”lead role’’ in making the OMAP 5 device on… Read More

Who Needs a 3D Field Solver for IC Design?

Inroduction

In the early days we made paper plots of an IC layout then measured the width and length of interconnect segments with a ruler to add up all of the squares, then multiplied by the resistance per square. It was tedious, error prone and took way too much time, but we were rewarded with accurate parasitic values for our SPICE… Read More

Wanted: FPGA start-up! …Dead or Alive?

The recent announcement from Tabula about the $108 million raised in its Series D round of funding is putting the focus on FPGA technology, and FPGA startups in particular. Who are these FPGA startups, what is their differentiation, where is the innovation, in the product or the business model?

When you say FPGA, you first think:… Read More

Build a 100% Python-based Design environment for Large SoC Designs