I will share with you some strategic information released by Cadence last week about their IP strategy, more specifically about the launch of the DDR4 Controller IP. And try to understand Cadence strategy about Interface IP in general (USB, PCIe, SATA, DDRn, HDMI, MIPI…) and how Cadence is positioned in respect with their closest and more successful competitor in this field, Synopsys.

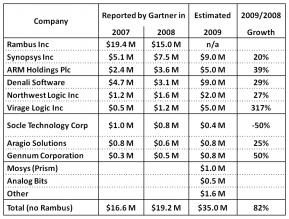

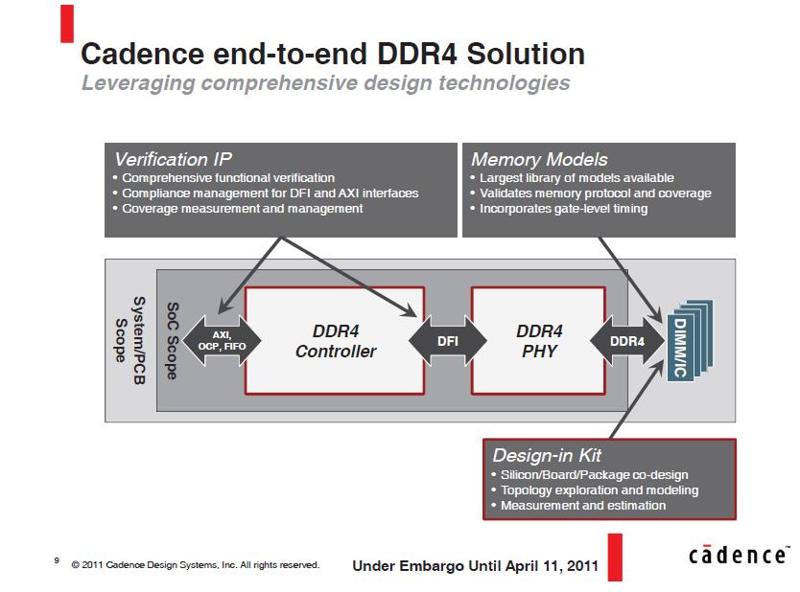

When Cadence has acquired Denali for $315M, less than one year ago, one of the nuggets was the DDRn controller IP product line built by Denali during the last 10 years. Denali’ DDR controller IP was well known within the industry, doing pretty well with sales in 2009 estimated to be slightly less than $10M (even if Denali was one of the very few companies who constantly report to Gartner DDR Controller IP business results below the reality!). Their product was nice, but still based on a Soft PHY, making life more complicated for the designer having to integrate it. Synopsys DDR Controller IP (coming from the acquisition of MOSAID in 2007) was already based on a hard PHY, as well as Virage’ product (coming from the acquisition of INGOT in 2005). That’s why Denali had to build a partnership with MOSYS (in fact Prism Circuit before to be acquired in 2009) to offer a solution based on a hard PHY (from MOSYS) and their DDR3 Controller. Before the acquisition of Denali by Cadence (and Virage by Synopsys, by the way) in May 2010, the DDR Controller IP market was growing fast, and very promising, as we can see on the two figures.

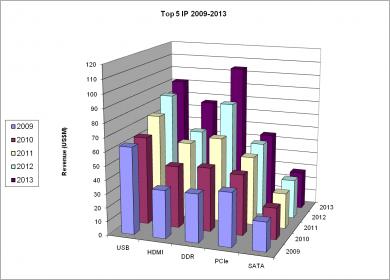

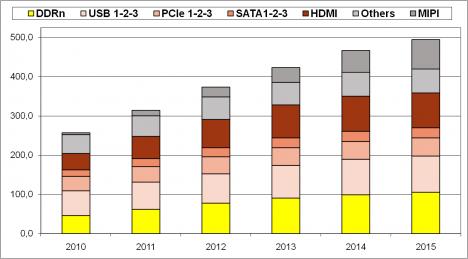

In fact, if the number of ASIC design start is declining, the proportion of SoC is growing faster, so the net count of ASIC integrating a processor (or Controller, DSP) core is growing. When you integrate a processor, you need to access an external memory (the cost of embedded DRAM being prohibitive) so you need t integrate a DDRn Controller. Considering the ever increasing memory Interface frequency, and the related difficulty to build a DDRn Controller in-house, the make vs buy question leads more frequently to an external solution, or to buy an IP. This is why the forecast for the DDR Controller IP market, even the more conservative, shows a x3 multiplication during the next 3 years. And when we compare the DDR IP market with the other Interface IP market, we expect it to be the faster growing market, as we can see on the first figure.

With this history in mind, you better understand why it was important for Cadence to be the first to launch a DDR4 Controller IP. Proposing a hard PHY option is a way to catch up with Synopsys, who offer hard PHY systematically for the DDR IP product. The lack of such a hard PHY was a weakness of the Denali DDRn IP product line, this explain why Denali had built a partnership with Prism Circuit in April 2009 to offer a complete solution based on a (soft) Controller from Denali and a (hard) PHY from Prism Circuit. Ironically, both companies have been acquired in the meantime…

If we look at the IP market, at least at the Interface IP segments (USB, PCIe, SATA, HDMI, DDRn, MIPI…), we see that the positioning of Cadence is pretty weak, compared with Synopsys. Cadence is supporting DDRn segment, thanks to Denali product line, the PCIe segment (in fact restricted to PCIe Gen-3)… and that’s it. When Synopsys is active in all the above mentioned segments, with a dominant position (more than 50% market share) in USB, SATA, PCIe, DDRn and a decent (but unknown) position in HDMI and MIPI. Moreover, Cadence strategy as presented during IP-SoC 2010 last December in Grenoble, which was to build a complete offer in the Interface IP market through partnership with existing IP vendors (if you prefer, offering a solution coming from 3[SUP]rd[/SUP] party instead of internally developed) has completely vanished. This will certainly leave the door open for Synopsys to consolidate their dominant position, and build a product line of more than $250M on a $500M market (IPnest evaluation of the Interface IP market in 2015). To summarize, Mentor Graphics gave up in 2005 on the IP market, and the last announcement from Cadence means that they will attack 20% only of this market (the DDRn IP) and give up on the remaining 80%, which will represent $400M in 2015.

The study of the Interface IP market: analysis of 2004-2009 results and Forecast for 2010-2015 can be found on:http://www.ip-nest.com/index.php?page=wired

This survey is unique and very complete, looking at each interface (USB1,2, USB3, PCIe, SATA, DDRn, HDMI, MIPI, DisplayPort and more) and proposing a forecast for 2010-2015.

It has been sold to several IP vendors (Cadence (!), Mosys, Cast, Evatronix, HDL DH…) and the KSIA in Corea. Please contacteric.esteve@ip-nest.com if you are interested…

From the Selfie to Samantha: The Next Trillion-Dollar Behavior