Data rates have doubled, but validation methods have not kept pace. As PCIe, DDR, and multi-terabit optical interconnects evolve, engineers are encountering signal integrity challenges much earlier in the design process.

Join Niels Fache, Senior Vice President and General Manager of Design Engineering Software at Keysight,… Read More

As semiconductor design pushes into increasingly complex territory, driven by Ai, ML, HPC, and heterogeneous system architectures, designers are challenged to balance performance, power, and time-to-market pressures. In this landscape, network-on-chip (NoC) architectures have emerged as a foundational building block… Read More

High-speed signals enable electronic systems by using memory interfaces, SerDes channels, data center backplanes and connectivity in automobiles. Challenges arise from signal distortions like inter-symbol interference, channel loss and dispersion effects. Multi-gigabit data transfer rates in High-Bandwidth Memory… Read More

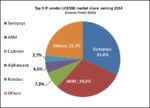

Design IP revenues achieved $8.5B in 2024 and this is an all-time-high growth of 20%. Wired Interface is still driving Design IP growth with 23.5% but we see the Processor category also growing by 22.4% in 2024. This is consistent with the Top 4 IP companies made of ARM (mostly focused on processor) and a team leading wired interface… Read More

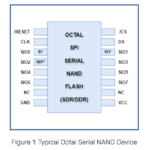

As the automotive industry continues to evolve, the demands for high-capacity, high-speed storage solutions are intensifying. Autonomous vehicles and V2X (Vehicle-to-Everything) communication systems generate and process massive amounts of data, necessitating advanced storage technologies capable of meeting these… Read More

S2C, a leading provider of FPGA-based prototyping solutions, has helped a client achieve high-performance secure GPU chip verification. With the help of S2C’s Prodigy prototyping solution, the client was able to start software development and hardware-software co-design early, leading to accelerated time-to-market… Read More

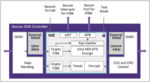

News of hackers breaking into systems is becoming common place these days. While many of the breaches reported to date may have been due to security flaws in software, vulnerabilities exist in hardware too. As a result, the topic of security is getting increased attention within the semiconductor industry around system-on-chip… Read More

Before the advent of the digitized society and computer chips, things that needed protection were mostly hard assets such as jewelry, coins, real estate, etc. Administering security was simple and depended on strong guards who provided security through physical means. Then came the safety box services offered by financial … Read More

Introduction:

The advancements in deep submicron technology and adding multiple functionalities to reduce costs combined with scaling existing operations means that SoC designs become ever more complex. The biggest driving factors to go below the 16nm process node are the decrease in power and the increase in performance … Read More

Sondrel just released a position paper on how to model and design a complex ASIC. We have been following Sondrel for the past year and I have found their collateral to be excellent. Here is the position paper overview, a description of the new Sondrel modeling tool, the 10 steps, and of course a link to download the paper:

Overview

It… Read More