I went to part of the Linley Tech Mobile Conference. This is the current incarnation of what started life as Michael Slater’s Microprocessor Report, and the twice-yearly Microprocessor Forum. These very technical analysis organizations seem to work well when they are a small group of analysts working together to cover… Read More

From Space-Central to Space-Time Balanced - A Perspective for Moore’s Law 2.0 and A Holistic Paradigm for EmergenceA friend of SemiWiki published an article on…Read More

From Space-Central to Space-Time Balanced - A Perspective for Moore’s Law 2.0 and A Holistic Paradigm for EmergenceA friend of SemiWiki published an article on…Read More The RISC-V and Open-Source Functional Verification ChallengeMost of the RISC-V action at the end…Read More

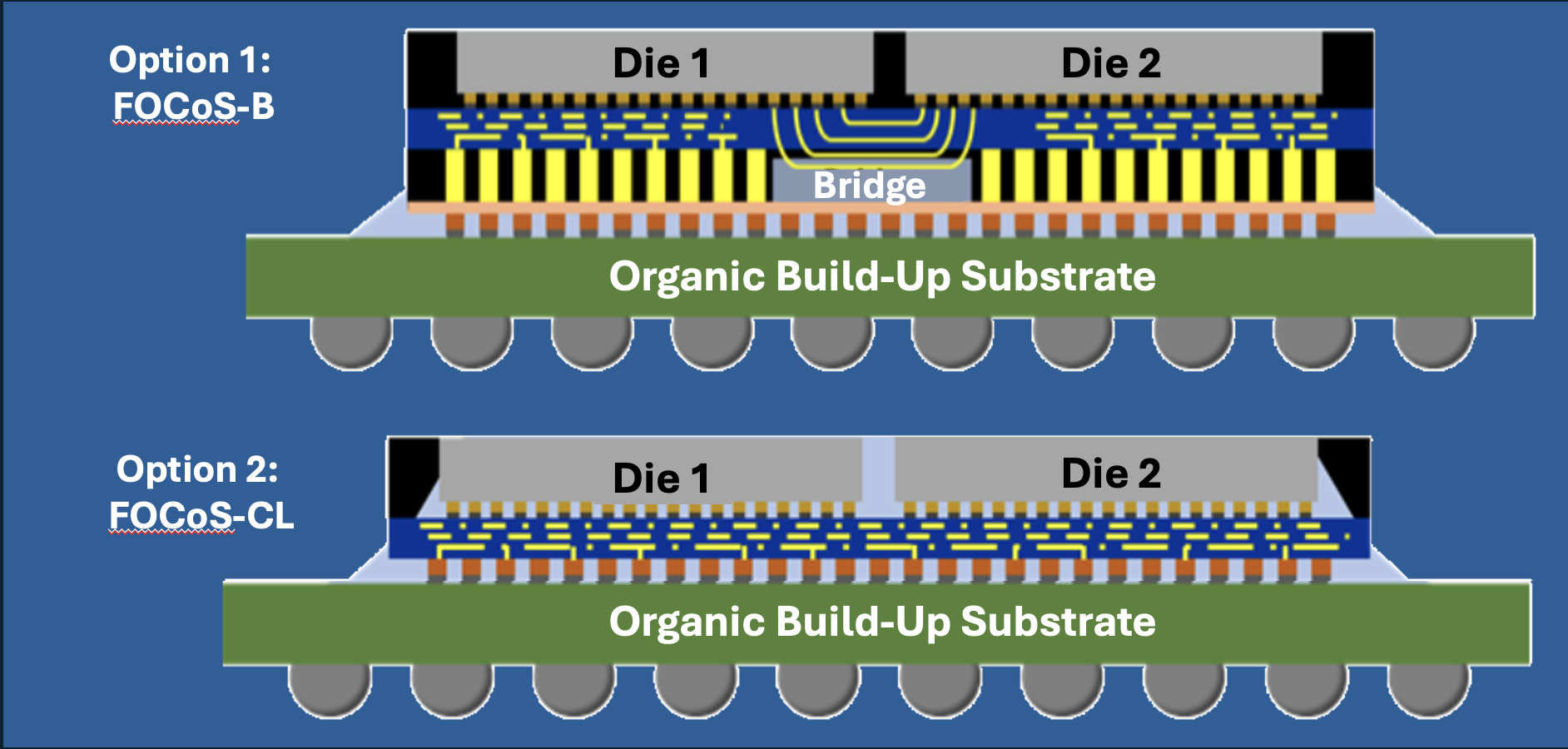

The RISC-V and Open-Source Functional Verification ChallengeMost of the RISC-V action at the end…Read More Sarcina Democratizes 2.5D Package Design with Bump Pitch Transformers2.5D package design is rapidly finding its stride…Read More

Sarcina Democratizes 2.5D Package Design with Bump Pitch Transformers2.5D package design is rapidly finding its stride…Read More Addressing Reliability and Safety of Power Modules for Electric VehiclesAs electric vehicles (EVs) gain widespread adoption, safety,…Read More

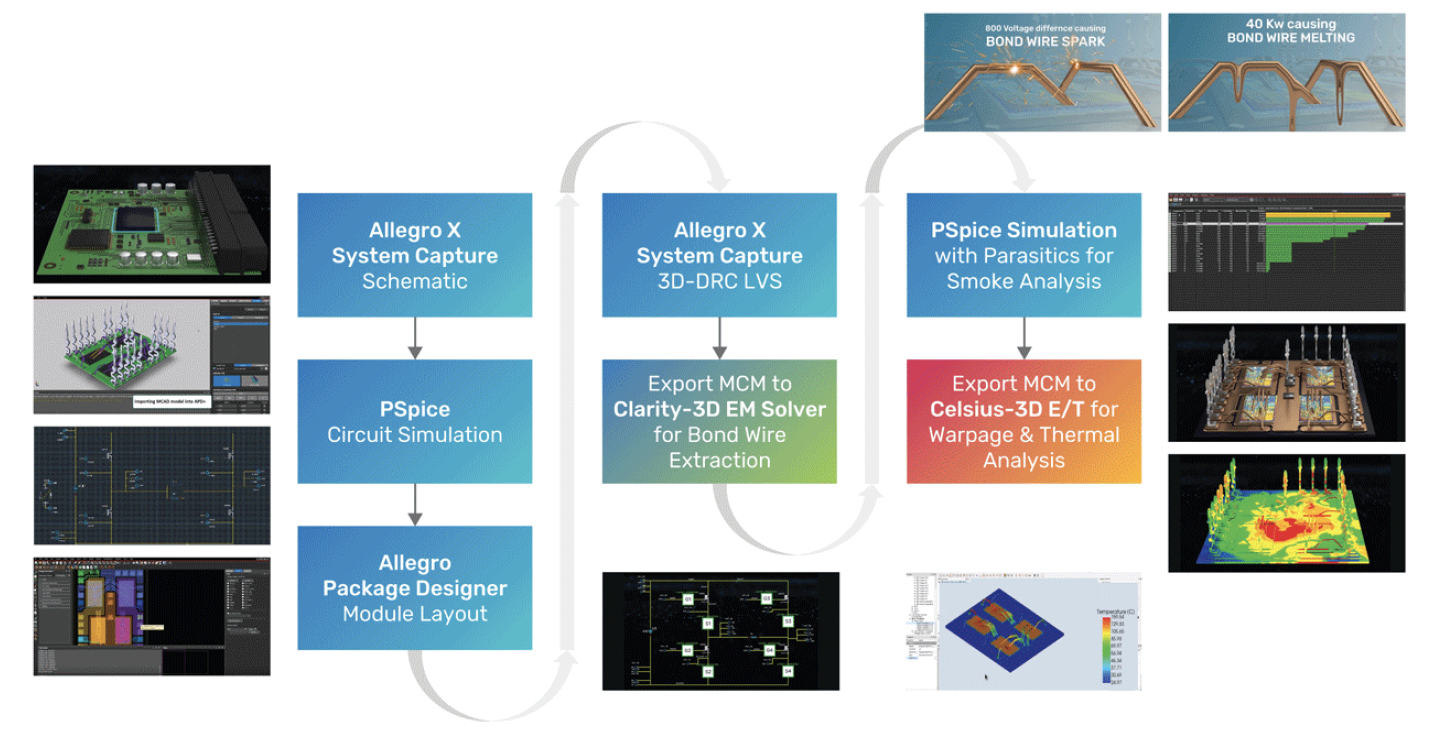

Addressing Reliability and Safety of Power Modules for Electric VehiclesAs electric vehicles (EVs) gain widespread adoption, safety,…Read MoreAnalog Circuit Optimization

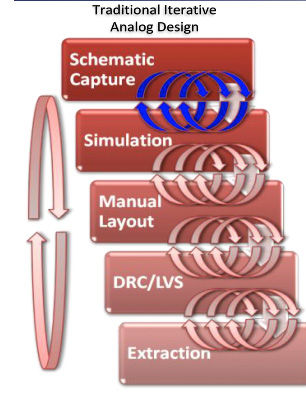

Gim Tan at Magma did a webinar on analog circuit optimization, so I watched it today to see what I could learn about their approach. Gim is a Staff AE, so not much marketing fluff to wade through in this webinar.

The old way of designing custom analog circuits involves many tedious and error prone iterations between front-end (Schematic… Read More

Changing your IC Layout Methodology to Manage Layout Dependent Effects (LDE)

Smaller IC nodes bring new challenges to the art of IC layout for AMS designs, like Layout Dependent Effects (LDE). If your custom IC design flow looks like the diagram below then you’re in for many time-consuming iterations because where you place each transistor will impact the actual Vt and Idsat values, which are now a … Read More

Intel Postgame Q1 2012 Earnings

Listening to the Intel earnings call yesterday and then reviewing the transcript last night, I came away with two thoughts that I think are key to understanding where the PC and mobile industry… Read More

ARM Seahawk

I wrote on Monday about ARM’s Processor Optimization Packs (POPs). In Japan they announced yesterday the Seahawk hard macro implementation in the TSMC 28HPM process. It is the highest performance ARM to date, running at over 2GHz. It is a quad-core Cortex A15.

The hard macro was developed using ARM Artisan 12-track libraries… Read More

Smart mobile SoCs: Qualcomm

In the opener to this series, I alluded to a company designing their own approach, and it goes way beyond the graphics core in their solution. Qualcomm is unique in a holistic approach to a smart mobile device with their vertically integrated chipset, the Snapdragon S4.… Read More

Previewing Intel’s Q1 2012 Earnings

Since November of 2011 when Intel preannounced it would come up short in Q4 due to the flooding in Thailand that took out a significant portion of the HDD supply chain, the analysts on Wall St. have been in the dark as to how to model 2012. Intel not only shorted Q4 but they effectively punted on Q1 as well by starting the early promotion… Read More

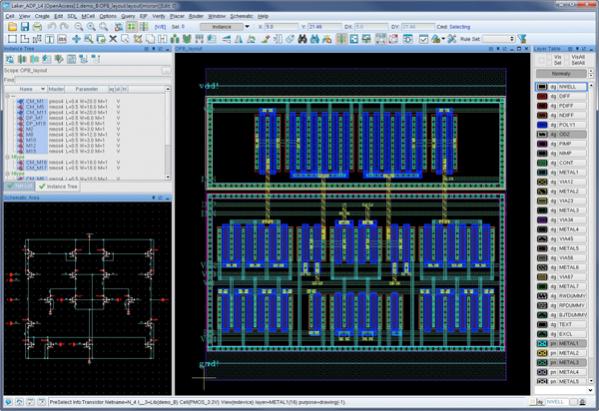

Laker Wobegon, where all the layout is above average

TSMC’s technnology symposium seems to be the new time to make product announcements, with ARM and Atrenta yesterday and Springsoft today.

There is a new incarnation of Springsoft’s Laker layout family, Laker[SUP]3[/SUP] (pronounced three, not cubed). The original version ran on its own proprietary database.… Read More

Soft Error Rate (SER) Prediction Software for IC Design

My first IC design in 1978 was a 16Kb DRAM chip at Intel and our researchers discovered the strange failure of Soft Errors caused by Alpha particles in the packaging and neutron particles which are more prominent at higher altitudes like in Denver, Colorado. Before today if you wanted to know the Soft Error Rate (SER) you had to fabricate… Read More

Atrenta’s Spring Cleaning Deal

Atrenta is having a special offer to let you “spring clean” your IP for free. They are providing two weeks of free access to the Atrenta IP kit starting from today, April 16th, until the end of May. During this period, qualified design groups in the US will be able to use the kit for two consecutive weeks to “spring… Read More

AI Semiconductor Market