TSMC’s technnology symposium seems to be the new time to make product announcements, with ARM and Atrenta yesterday and Springsoft today.

TSMC’s technnology symposium seems to be the new time to make product announcements, with ARM and Atrenta yesterday and Springsoft today.

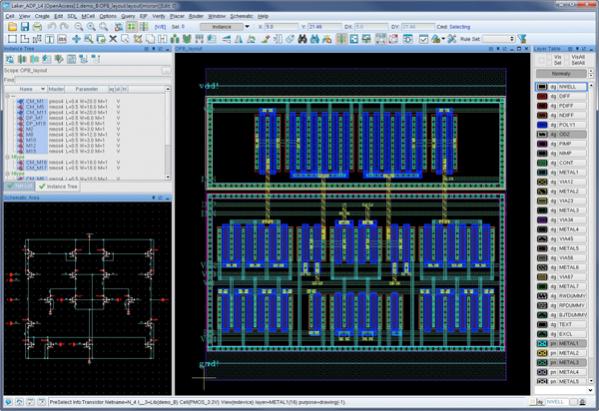

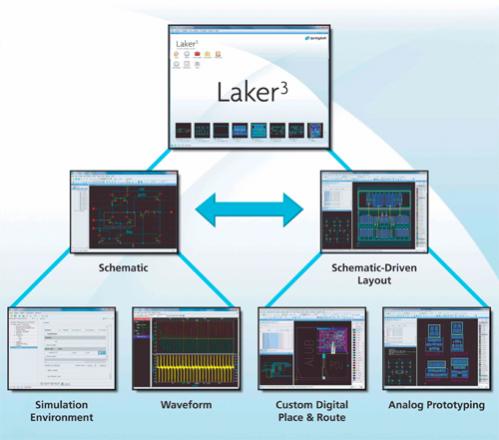

There is a new incarnation of Springsoft’s Laker layout family, Laker[SUP]3[/SUP] (pronounced three, not cubed). The original version ran on its own proprietary database. The second version added openAccess to the mix, but with an intermediate layer to allow both databases to work. Laker[SUP]3[/SUP] bites the bullet and uses openAccess as its only native database. This gives it the performance and capacity for 28nm and 20nm flows.

There are a lot of layout environments out there. Cadence, of course, has Virtuoso. Synopsys already had one of their own and then with the acquisition of Magma have a second one. Mentor is in the space. Some startups are in the space too. Springsoft had an executive pre-release party on Thursday last week (what EDA tool doesn’t go better with a good Chardonnay) and one senior person (who had better remain nameless since I don’t think it was meant to be an official statement of his employer) said that he thought that by the time we get to 20nm there are only going to be a couple of layout systems with the capability to remain standing and Springsoft would be one.

There are a lot of layout environments out there. Cadence, of course, has Virtuoso. Synopsys already had one of their own and then with the acquisition of Magma have a second one. Mentor is in the space. Some startups are in the space too. Springsoft had an executive pre-release party on Thursday last week (what EDA tool doesn’t go better with a good Chardonnay) and one senior person (who had better remain nameless since I don’t think it was meant to be an official statement of his employer) said that he thought that by the time we get to 20nm there are only going to be a couple of layout systems with the capability to remain standing and Springsoft would be one.

There are three big new things in Laker[SUP]3[/SUP]. The first is the switch to openAccess. But they didn’t just switch they also re-wrote all the disc access part so that there is a performance increase of 2-10X on things like reading in designs or streaming out gds2. But many intermediate things are also reading and writing stuff to disk so it is not just the obvious candidates that speed up.

The second is that the previous versions of Laker had a table driven DRC. That has been completely re-written since just simple width and spacing type rules are no longer adequate (‘simple’ is not a word that anyone would use about 28nm design rules, let alone 20nm with double patterning and other weird stuff). The new DRC can handle these types of rules, but it is not positioned as a signoff DRC, it is used by all the rule-driven functions and by place and route. On the “trust but verify” basis, Calibre is also built into Laker in the form of Calibre RealTime that runs continuously in the background giving instant feedback using the signoff rule deck. Since no designer can actually comprehend design rules any more, this is essential. The alternative, as one customer of another product complained, is having to stream out the whole design every 15 minutes and kick off a Calibre run.

The third big development is an analog prototyping flow. One big difference is that most constraint generation (to tell the placer what to do) is automatically recognized as opposed to the user having to provide a complex text file of constraints. Symmetrical circuits are recognized by tracing current flow, common analog and digital subcircuits such as current mirrors are recognized. The library of matched devices is extendible so that prototyping flow gets smarter over time as the idiosyncrasies of the designer, design or company get captured. There have been numerous attempts to improve the level of automation in analog layout, the hillside is littered with the bodies. This looks to me as if it manages to strike a good balance between automating routine stuff while still leaving the designer in control (analog design will never be completely automatic, let’s face it).

Laker for a time was regarded somewhat unfairly as “only used by people in Taiwan” where admittedly it has become the dominant tool. But two of the top five fabless semiconductor companies have standardized on Laker, and five of the top ten semiconductor companies are using it. And the hors d’ouvres in the edible spoons at the launch party were pretty neat.

Laker for a time was regarded somewhat unfairly as “only used by people in Taiwan” where admittedly it has become the dominant tool. But two of the top five fabless semiconductor companies have standardized on Laker, and five of the top ten semiconductor companies are using it. And the hors d’ouvres in the edible spoons at the launch party were pretty neat.

More details on Laker[SUP]3[/SUP] are here.

Solving the EDA tool fragmentation crisis