You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

I was asked to give a talk at the 2021 ISS conference and the following is a write up of the talk.

The title of the talk is “Logic Leadership in the PPAC era”.

The talk is broken up into three main sections:

- Background information explaining PPAC and Standard Cells.

- A node-by-node comparisons of companies running leading edge logic

…

Read More

I have seen several articles recently discussing foundry wafer selling prices for leading edge wafers, these articles all quote estimates from a paper by the Center for Security and Emerging Technology (CSET). The paper is available here.

My company IC Knowledge LLC is the world leader in cost and price modeling of semiconductors… Read More

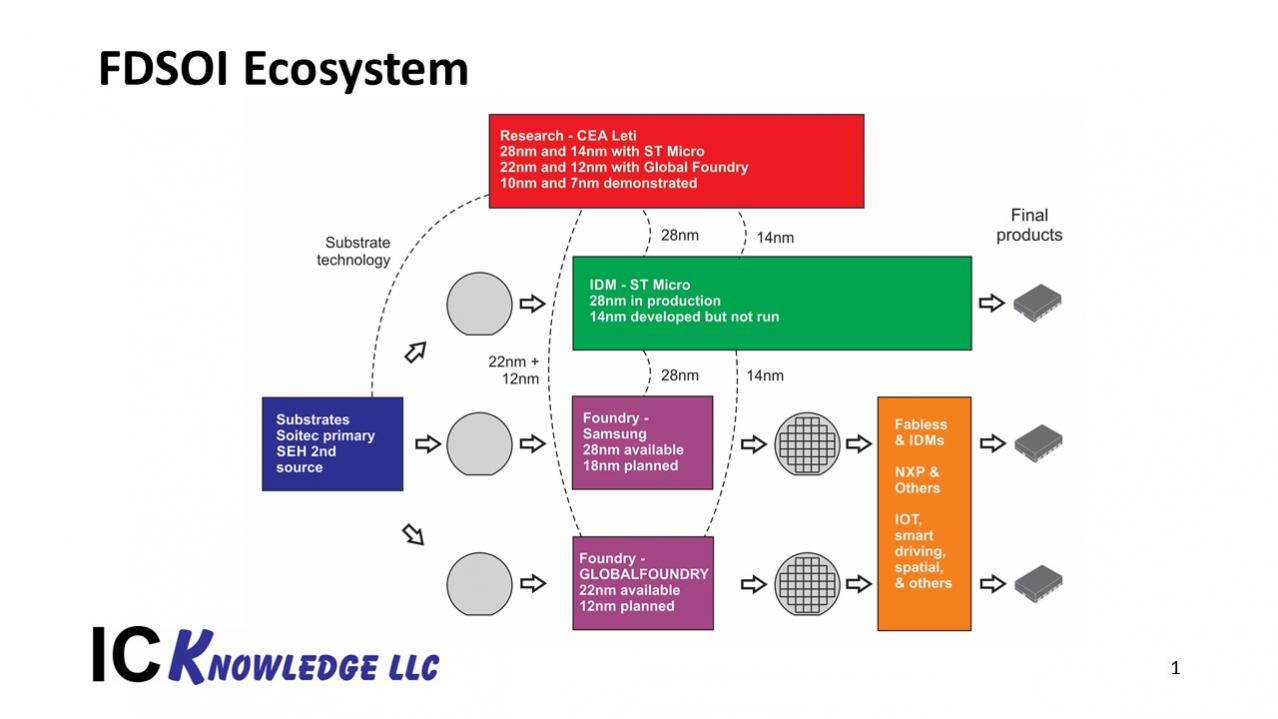

FDSOI is gaining traction in the market place. At their foundry forum in May, Samsung announced they have 17 FDSOI products in high volume manufacturing (you can read Tom Dilliger’s write up of the Samsung Foundry Forum here). At SEMICON West in July, GLOBALFOUNDRIES (GF) announced FDSOI design wins worth $2 billion dollars in … Read More

At Semicon West last week I attended presentations by Soitec and CEA Leti, and had breakfast with CEA Leti CEO Marie Semeria, key members of the Fully Depleted Silicon On Insulator (FDSOI) ecosystem. I have also seen some comments in the SemiWiki forum lately that make me believe there is some confusion on the roles of different companies… Read More

The cost trend for leading edge semiconductor technologies is a subject of some controversy in the industry. Cost is a complex issue with many interacting factors and much of the information out in the industry is in my opinion misleading or incorrect. In this article, I will discuss each of the factors as well as present a view of … Read More

Recently I published two blogs on Fully Depleted Silicon On Insulator (FDSOI) and the potential the technology shows for a variety of low power and wireless applications. In order to produce FDSOI devices, the device layer has to be thin enough to ensure the device is fully depleted and ideally the buried oxide has to be thin enough… Read More

18 months ago Renesas announced they were prototyping their SG-MONOS eFlash on 28nm, and at the time we said it would be a couple of years before actual product. Yesterday, Renesas revealed their partner in this effort is TSMC – no surprise – and hinted things are moving, with better performance than expected but on a longer qualification… Read More

On Tuesday, July 12th at SEMICON West I had an opportunity to sit down with Marie Semeria, the CEO of Leti and discuss the status and future of FDSOI. Leti pioneered FDSOI 15 years ago and has been the leading FDSOI research ever since.

Two years ago Leti and ST Micro demonstrated products on 28nm that are cost competitive with bulk technology.… Read More

IC design challenges are different at advanced nodes like 7nm, so to learn more about the topic I attended a panel luncheon at DAC sponsored by Cadence. The moderator was both funny and technically astute, quite the rare combination, so kudos to Professor Rob Rutenbar, a former Neolinear guy now at the University of Illinois. Panelists… Read More

A little over a month into 2016 and we already have a raft of FD-SOI news from Samsung, GlobalFoundries, NXP/Freescale, Renesas and more. Quite a bit of it came out of the recent SOI Consortium forum in Tokyo. Many of the presentations are now available on the SOI Consortium website (click here to see what’s there) – but keep checking… Read More