Introduction

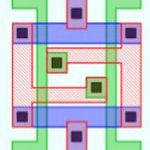

IC designs go through a layout process and then a verification of that layout to determine if the layout layer width and spacing rules conform to a set of manufacturing design rules. Adhering to the layout rules will ensure that your chip has acceptable yields.

At the 28nm node a typical DRC (Design Rule Check) deck will… Read More

Tag: 28nm

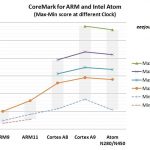

ARM vs Intel…Performance? Power? OS support? Or ubiquity?

This blog was posted 10 months ago, and the comments have made it much more interesting! Don’t miss the various comments at the back. Also feel free to let us know if you think the status, in this ARM vs Intel “war” has changed a lot since March 2011. Do you really think Intel has catch up with ARM in the mobile industry?… Read More

Getting Real Time Calibre DRC Results

Last week I met with Joseph Davis, Ph.D. at Mentor Graphics in Wilsonville, Oregon to learn about a new product designed for full-custom IC layout designers to improve productivity.

The traditional flow for full-custom IC layout designers has been nearly unchanged for decades:

- Read a schematic or use Schematic Driven Layout

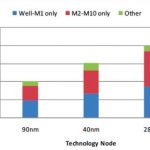

TSMC Versus The FabClub!

The Common Platform Technology Forum last week was not well attended, less than half than the GlobalFoundries Conference. It was deja vu of previous CP forums but there were a couple of surprises to go with the disappointment. The lunch line was long, but fortunately I was escorted to the press lunch featuring VIP’s from Samsung,… Read More

Getting to the 32nm/28nm Common Platform node with Mentor IC Tools

Last week I talked with two experts at Mentor about the challenges of getting IC designs into the 32nm/28nm node on the Common Platform (IBM, GLOBALFOUNDRIES and Samsung). Global Foundries issued a press release talking about how the four major EDA companies have worked together to qualify EDA tools for this node.

Sudhakar Jilla,… Read More