Apple, Google, and FaceBook are making significant investments in artificial intelligence (deep learning) and other advertising (snooping) enabling technology to better serve (exploit) their customers (us) and make trillions of dollars for their offshore accounts. This reminds me (in a very creepy way) of the TV series “Person… Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read More

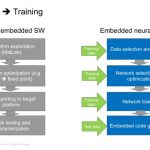

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read MoreNeural Networks Ready for Embedded Platforms

If you are not yet familiar with the term Convolutional Neural Networks, or CNN for short, you are certainly bound to become in the year ahead. Using Artificial Intelligence in the form of CNN is on the verge of replacing a large number of computing tasks, especially those involving recognizing things such as sounds, shapes, objects,… Read More

S2C opens up FPGA prototyping for PCIe fabrics

Reconfigurable computing began with FPGA cards dropped into expansion slots in workstations. FPGA-based prototyping vendors tended away from that model as interconnect speeds rose and cabling complexity between modules increased. Much faster PCIe interfacing and bigger FPGAs mean revisiting the concept.… Read More

Synopsys at DVCon 2016

It’s that time of year again – DVCon starts on Monday Feb 29[SUP]th[/SUP] and as always should be a packed event. Synopsys plans a big showing, in the exhibit hall, in a sponsored lunch, at tutorials and in papers. Time to get your conference shoes on and go check them out – I plan to be there all week.

One of the most obvious things you will… Read More

Should terrorists prefer iPhone (thanks to privacy)?

The case between Apple and the FBI may not be as limpid as it could be. If you ask me if Apple, or any US or Europe based supplier of high tech system should help the FBI (or any similar organization) and provide the technical support needed to extract information belonging to a terrorist, my answer would be definitely YES.

I don’t know… Read More

TSMC and Intel on the Long Road to EUV

Today is the first day of the SPIE Advanced Lithography Conference and Extreme Ultraviolet (EUV) updates were a big focus.… Read More

SoC power management a study in transition latency

Apple’s recent bout with ‘Batterygate’ highlighted just how important dynamic power management can be. Our last Sonics update looked at using their NoC to manage power islands; this time, we look at their research progress on architectural measures for power management.… Read More

A Brief History of Open-Silicon

In 2003, when Open-Silicon was founded there was a growing need for flexible and innovative ways of getting chip designs manufactured. Semiconductor companies, given the alternatives of COT or traditional ASIC, often were looking for more flexibility without the huge investment and risk of going COT. Let’s look at how Open-Silicon… Read More

FinFET For Next-Gen Mobile and High-Performance Computing!

Evolving opportunities call for new and improved solutions to handle data, bandwidth and power. Moving forward, what will be the high-growth applications that drive product and technology innovation? The CAGRs for smartphone and data center continue to be very strong and healthy. … Read More

Advanced Micro Device’s New Polaris FinFET-Based Architecture Could Open New Doors

It seems of late like there is an unlimited thirst for GPU performance at the right power efficiency. Whether it is deep learning, object recognition, artificial intelligence, simulations, VR or AR, the industry desperately needs GPU improvements. Many within the graphics industry would agree that a new era of graphics performance… Read More

Solving the EDA tool fragmentation crisis