You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Blockchain and Artificial Intelligence are two of the hottest technology trends right now. Even though the two technologies have highly different developing parties and applications, researchers have been discussing and exploring their combination [6].

PwC predicts that by 2030 AI will add up to $15.7 trillion to the world… Read More

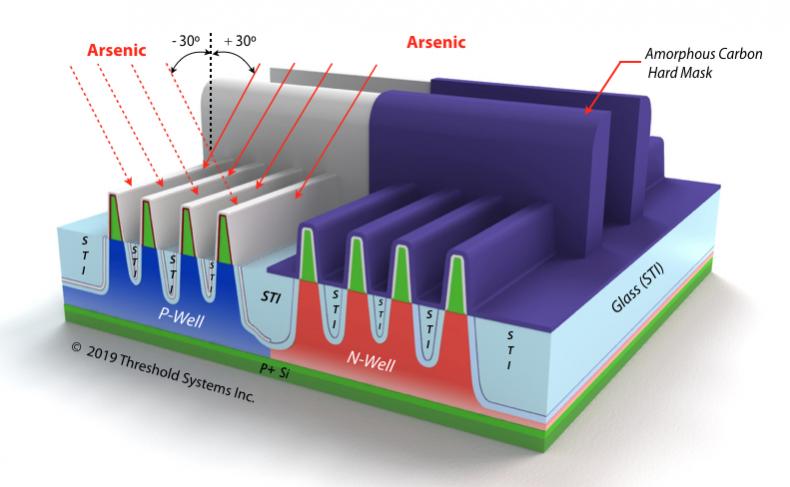

The problem of traditional FinFET Extension Implant doping concerns the awkward 3-dimensional structure of the fin. Because the Extension Implant defines the conductive electrical pathway between the Source/Drains and the undoped channel portion of the fin, it is essential that the fin be uniformly doped all three of its surfaces… Read More

Tesla Motors held an investor event at its Palo Alto headquarters. CEO Elon Musk and a series of Tesla executives announced a new in-house developed microprocessor (already in production and being deployed in Tesla vehicles) and its plans and progress toward autonomous vehicle operation.

Tesla Autonomy Day Live Stream

To be … Read More

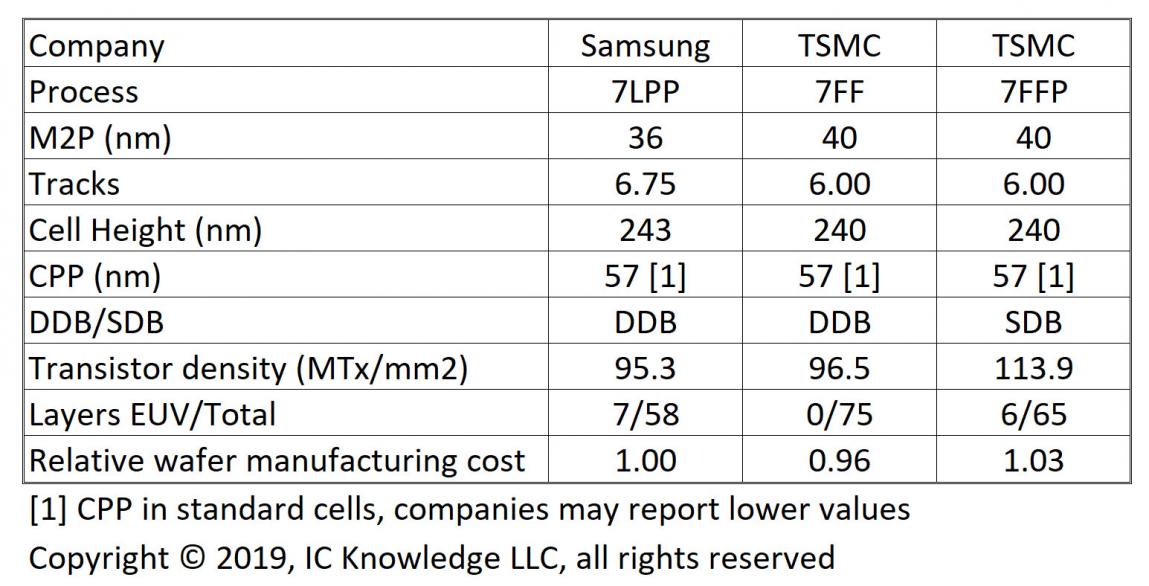

Samsung and TSMC have both made recent disclosures about their 5nm process and I though it would be a good time to look at what we know about them and compare the two processes.

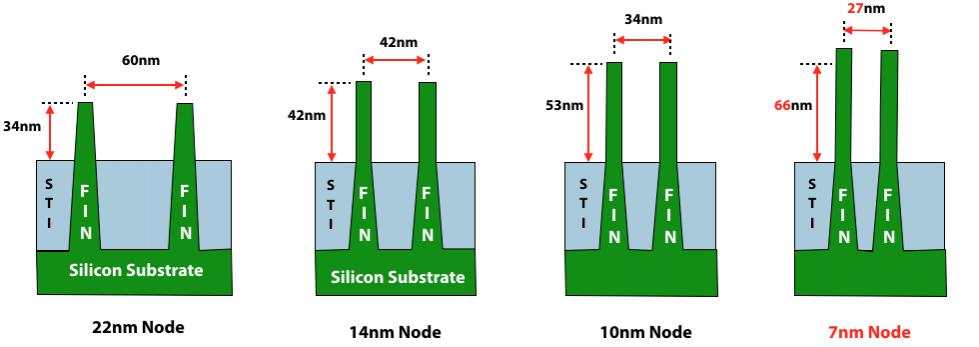

A lot of what has been announced about 5nm is in comparison to 7nm so we will first review 7nm.

7nm

Figure 1 compares Samsung’s 7LPP process to TSMC’s 7FF and 7FFP… Read More

To me the major idea of ISO 26262 compliance is ensuring that requirements can be traced throughout the entire design and verification process, including the use of IP blocks. The first market application that comes to mind with ISO 26262 is automotive, with its emphasis on safety because human lives are at stake. Since necessity… Read More

The use of hard masks instead of photoresist for the Extension implant is an effective way to optimize the amount of dopant that is retained along the fin sidewalls for those fins that border along photoresist edges (as discussed in Part 1 of this series).

However, hard masks do nothing to address the dominant problem driving steeper… Read More

The famous Olympic motto Citius, Altius, Fortius, which is the Latin words for “Faster, Higher, Stronger” to a considerable degree can be adapted to our electronics industry. Traditionally the fundamental metrics we used for measuring the quality of results (QoRs) are performance, power, and area (PPA). Amidst… Read More

At first glance, this seems like a ho-hum topic- just use whatever Arm or RISC-V solution you need – but think again. We’re now expecting to push an awful lot of functionality into these edge devices. Our imaginations don’t care about power, performance and cost; everything should be possible so let’s keep adding cool features.… Read More

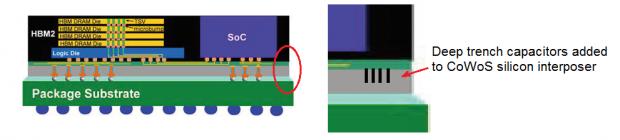

TSMC recently held their annual Technology Symposium in Santa Clara. Part 1 of this article focused on the semiconductor process highlights. This part reviews the advanced packaging technologies presented at the symposium.

TSMC has clearly made a transition from a “pure” wafer-level foundry to a supplier of complex integrated… Read More

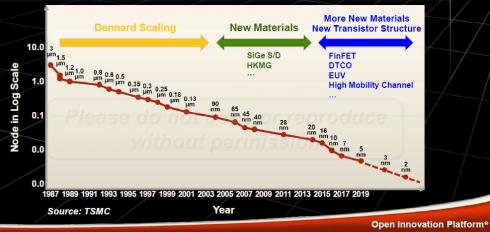

Each year, TSMC conducts two major customer events worldwide – the TSMC Technology Symposium in the Spring and the TSMC Open Innovation Platform Ecosystem Forum in the Fall. The Technology Symposium event was recently held in Santa Clara, CA, providing an extensive update on the status of advanced semiconductor and packaging… Read More

Solving the EDA tool fragmentation crisis