A switch this month to principles behind building effective agentic systems, going beyond simply a new way to stitch together tools, agents and orchestration, to deeper consideration of user experience and how we most effectively blend agentic with human-in-the-loop. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano… Read More

The Great Divide: A Tale of Three Hardware Emulation ArchitecturesHardware emulation arose as a necessity out of…Read More

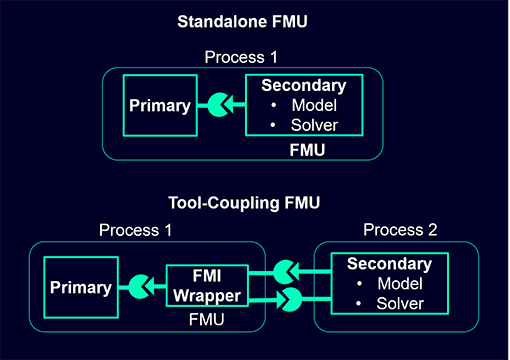

The Great Divide: A Tale of Three Hardware Emulation ArchitecturesHardware emulation arose as a necessity out of…Read More A Different Angle on Co-Simulation for SystemsCo-simulation, two or more simulations running concurrently in…Read More

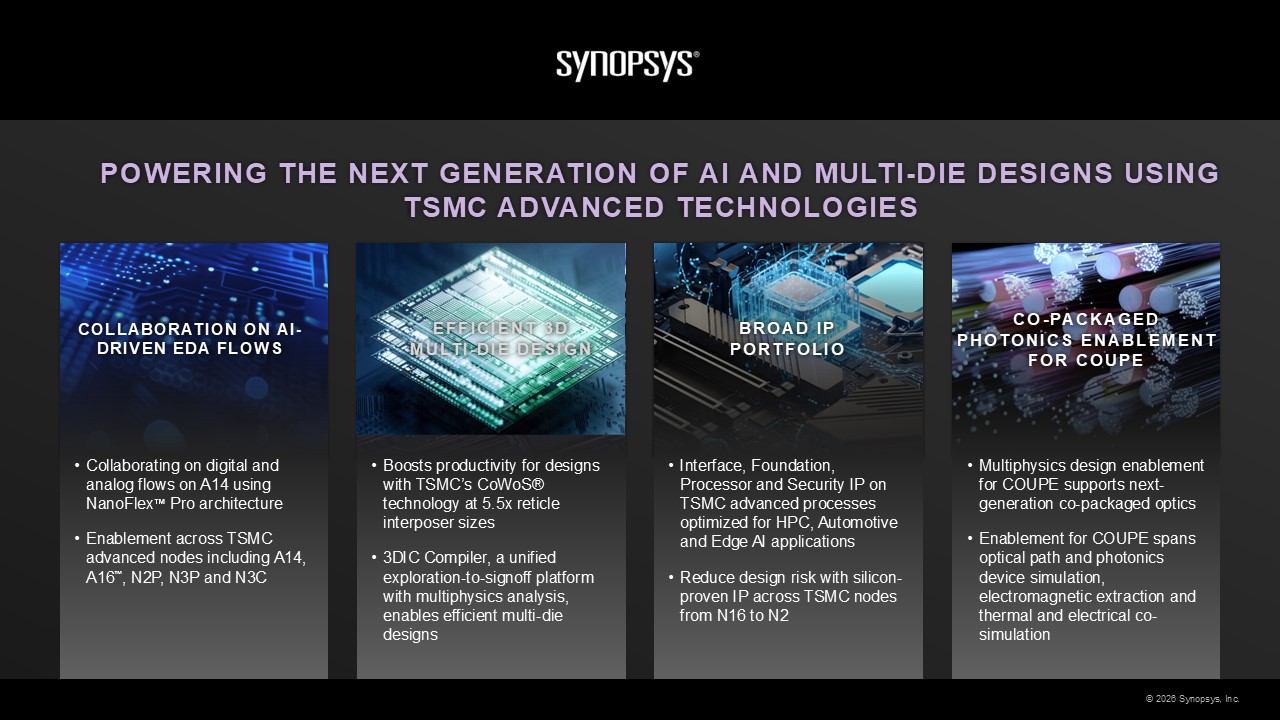

A Different Angle on Co-Simulation for SystemsCo-simulation, two or more simulations running concurrently in…Read More Synopsys and TSMC Deepen AI Design Alliance: What It MeansA recent announcement from Synopsys signals a meaningful…Read More

Synopsys and TSMC Deepen AI Design Alliance: What It MeansA recent announcement from Synopsys signals a meaningful…Read MoreScalable Network-on-Chip Enables a Modular Chiplet Platform

The semiconductor industry is undergoing a profound transformation as system complexity, performance expectations, and time-to-market pressures continue to rise. Traditional monolithic system-on-chip (SoC) designs are increasingly giving way to modular, chiplet-based architectures that enable flexibility, scalability,… Read More

The Shift to System-Level AI Drives Next-Generation Silicon

At its 2026 Technology Symposium, TSMC delivered a clear message: the AI era has entered a new phase. The primary constraint is no longer model capability, but the systems required to run those models at scale. Addressing this shift will demand significant advances in semiconductor technology, spanning compute, memory, interconnects,… Read More

All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single Die

The rapid evolution of wireless audio has placed unprecedented demands on system integration, power efficiency, and performance. Against this backdrop, the webinar “All-in-One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single Die” offers a timely and technically rich exploration of how modern semiconductor design… Read More

Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet Governance

By Dr. Moh Kolbehdari

Dr. Moh Kolbehdari is a Senior Lead Architect at Socionext, where he specializes in the industrialization of high-performance AI chiplets and 1.8-Tb/s interconnects. With over two decades of experience in SI/PI, electromagnetic field theory, and system-level architecture, he has been a pivotal force… Read More

SemiWiki Q&A with Julie Rogers, Executive Director, ESD Alliance

The Electronic System Design Alliance (ESD Alliance), a SEMI Technology Community, an international association of companies providing goods and services throughout the semiconductor design ecosystem, is a forum to address technical, marketing, economic and legislative issues affecting the entire industry. It acts … Read More

CEO Interview with Xianxin Guo of Lumai

Xianxin is the CEO and Co-Founder of Lumai, an Oxford University spin-out pioneering disruptive optical computing technologies for Al and data center acceleration. He brings over 15 years of experience in physics and engineering, and was previously an RCE 1851 Research Fellow, a prestigious fellowship whose past awardees … Read More

Podcast EP343: How Ethernet is Enabling Advances in AI with Dr. Mohan Kalkunte

Daniel is joined by Dr. Mohan Kalkunte, Vice President of Architecture & Technology in the Core Switch Products group at Broadcom, where he leads architecture for Ethernet switching and NIC products across data center, enterprise, and service provider markets. With over 35 years of industry experience his previous stints… Read More

SemiWiki Acquires IPnest!

After more than 15 years of collaboration with Dr. Eric Esteve and IPnest, SemiWiki has acquired the famed IP reports with Eric Esteve staying on through 2026 to ease the transition. Not only will SemiWiki provide the industry standard Interface IP and Design IP reports, SemiWiki will be expanding the depth and breadth of the coverage.… Read More

Elon Musk Needs to Put His Fab Money Where his Mouth is!

To me this is going to be one of the bigger Chicken Little moments in the history of semiconductors. Mostly because we are now a click driven society and the media is plagued by so called influencers that live and die by clicks. In my 40+ years as a semiconductor professional I have witnessed many of these Chicken Little moments with … Read More

Siemens U2U 3D IC Design and Verification Panel