Extreme ultraviolet (EUV) lithography targets sub-20 nm resolution using a wavelength range of ~13.3-13.7 nm (with some light including DUV outside this band as well) and a reflective ring-field optics system. ASML has been refining the EUV tool platform, starting with the NXE:3300B, the very first platform with a numerical

UX in Agentic Systems. Innovation in VerificationA switch this month to principles behind building…Read More

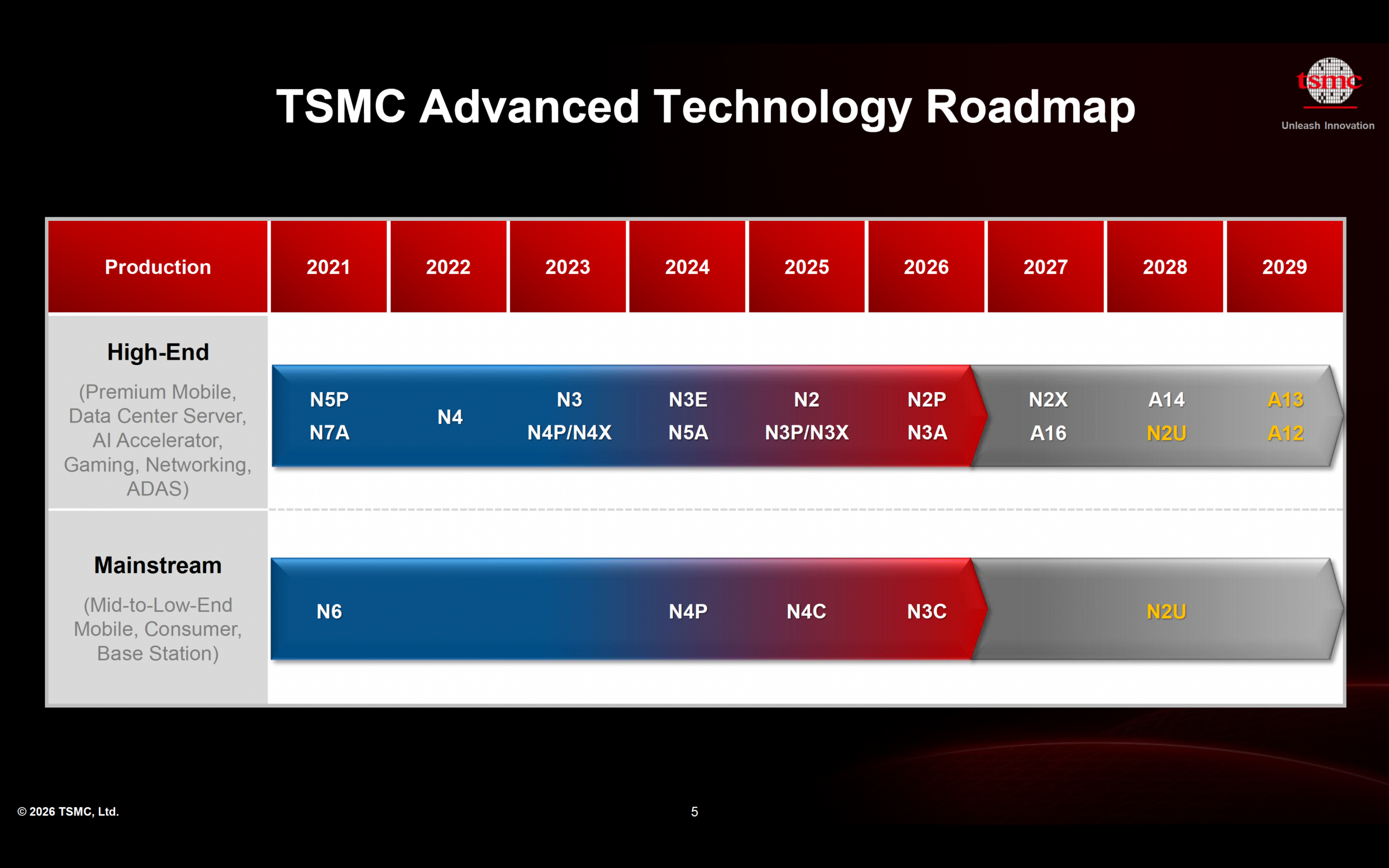

UX in Agentic Systems. Innovation in VerificationA switch this month to principles behind building…Read More The Shift to System-Level AI Drives Next-Generation SiliconAt its 2026 Technology Symposium, TSMC delivered a…Read More

The Shift to System-Level AI Drives Next-Generation SiliconAt its 2026 Technology Symposium, TSMC delivered a…Read More All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read More

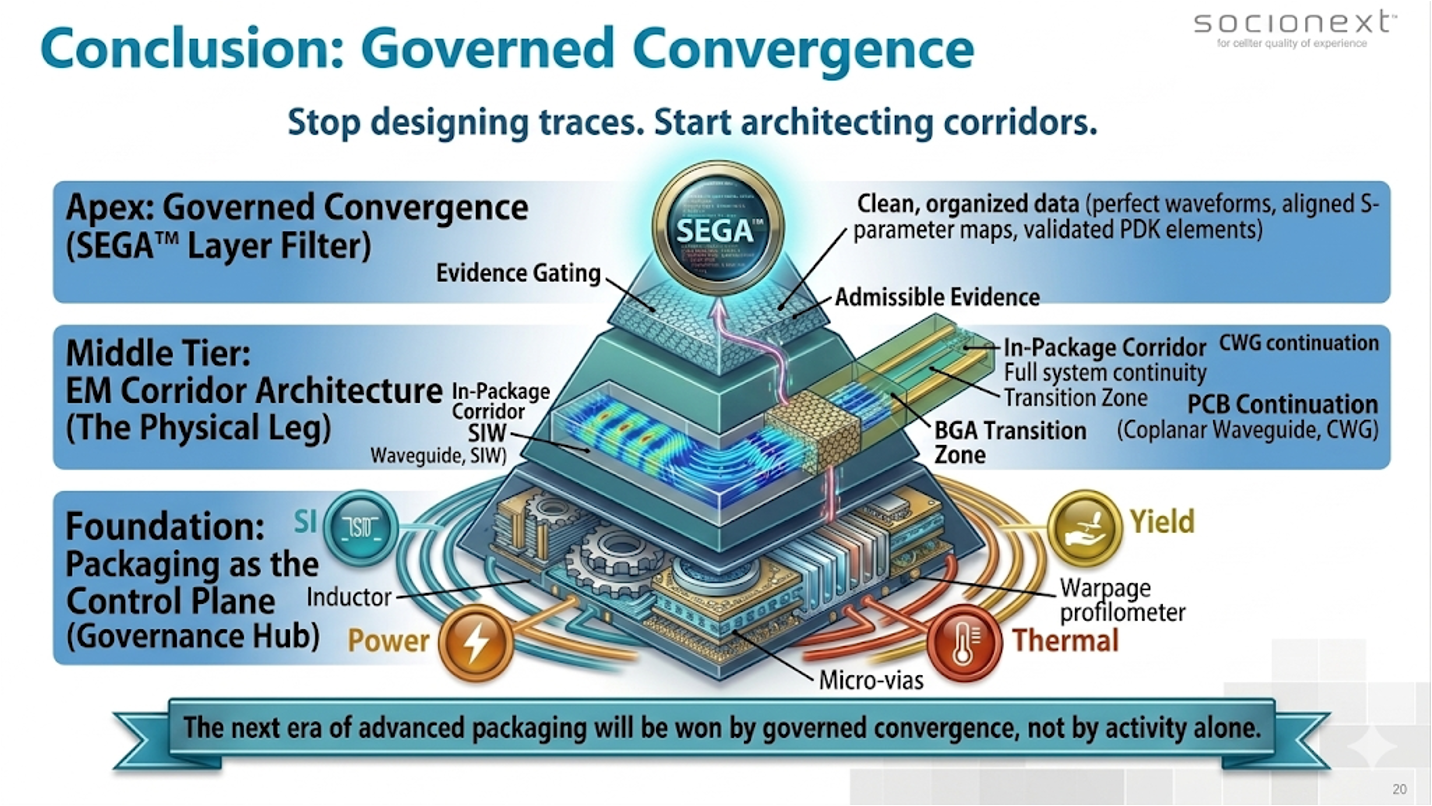

All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read More Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet GovernanceBy Dr. Moh Kolbehdari Dr. Moh Kolbehdari is…Read More

Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet GovernanceBy Dr. Moh Kolbehdari Dr. Moh Kolbehdari is…Read More SemiWiki Q&A with Julie Rogers, Executive Director, ESD AllianceThe Electronic System Design Alliance (ESD Alliance), a SEMI…Read More

SemiWiki Q&A with Julie Rogers, Executive Director, ESD AllianceThe Electronic System Design Alliance (ESD Alliance), a SEMI…Read MoreThere is No Easy Fix to AI Privacy Problems

Artificial intelligence – more specifically, the machine learning (ML) subset of AI – has a number of privacy problems.

Not only does ML require vast amounts of data for the training process, but the derived system is also provided with access to even greater volumes of data as part of the inference processing while in operation. … Read More

SPIE 2020 – Applied Materials Material-Enabled Patterning

I wasn’t able to attend the SPIE Advanced Lithography Conference this year for personal reasons, but Applied Materials was kind enough to set up a phone briefing for me with Regina Freed to discuss their Materials-Enabled Patterning announcement.

At IEDM Applied Materials (AMAT) tried to put together a panel across the entire… Read More

Why IP Designers Don’t Like Surprises!

If it’s your job to get a SoC design through synthesis, timing/power closure and final verification, the last thing you need are surprises in new versions of the IP blocks that are integrated into the design. If your IP supplier sends a new version, the best possible scenario is that this is only a small incremental change from… Read More

The Story of Ultra-WideBand – Part 4: Short latency is king

How Ultra-wideband aligns with 5G’s premise

In part 3, we discussed the time-frequency duality or how time and bandwidth are interchangeable. If one wants to compress in time a wireless transmission, more frequency bandwidth is needed. This property can be used to increase the accuracy of ranging, as we saw in part 3. Another very… Read More

Turbo-Charge Your Next PCIe SoC with PLDA Switch IP

SemiWiki has a new IP partner, PLDA and they bring a lot to the party. Peripheral component interconnect express (PCIe) is a popular high-performance data interface standard. Think GPUs, RAID cards, WiFi cards or solid-state disk (SSD) drives connected to a motherboard. The protocol offers much higher throughput than previous… Read More

Where have all the Leaders gone – a profile of T.J. Rodgers

Silicon Valley has morphed from the days of semiconductor fabs interspersed between strawberry farms, and 3:00 pm rush-hour traffic during the shift change for the fabrication facility engineers and technicians. The leadership of technology companies has also arguably devolved from people who inspired employees and stewarded… Read More

An Objective Hardware Security Metric in Sight

Security has been a domain blessed with an abundance of methods to improve in various ways, not so much in methods to measure the effectiveness of those improvements. With the best will in the world, absent an agreed security measurement, all those improvement techniques still add up to “trust me, our baby monitor camera is really… Read More

The Story of Ultra-WideBand – Part 3: The Resurgence

In Part 2, we discussed the second false-start of Ultra-WideBand (UWB) leveraging over-engineered orthogonal frequency-division multiplexing (OFDM) transceivers, launching at the dawn of the great recession and surpassed by a new generation of Wi-Fi transceivers. These circumstances signed the end of the proposed applications… Read More

Viewing the Largest IC Layout Files Quickly

The old adage, “Time is money”, certainly rings true today for IC designers, so the entire EDA industry has focused on this challenging goal of making tools that help speed up design and physical verification tasks like DRC (Design Rule Checks) and LVS (Layout Versus Schematic). Sure, the big three EDA vendors have… Read More

Solving the EDA tool fragmentation crisis