Silicon Catalyst is a unique startup incubator / accelerator that focuses exclusively on accelerating solutions in silicon (including chips, IP, MEMS & sensors). The organization has an extensive support infrastructure that includes preferred access to IP, design tools, business infrastructure and fab/assembly. … Read More

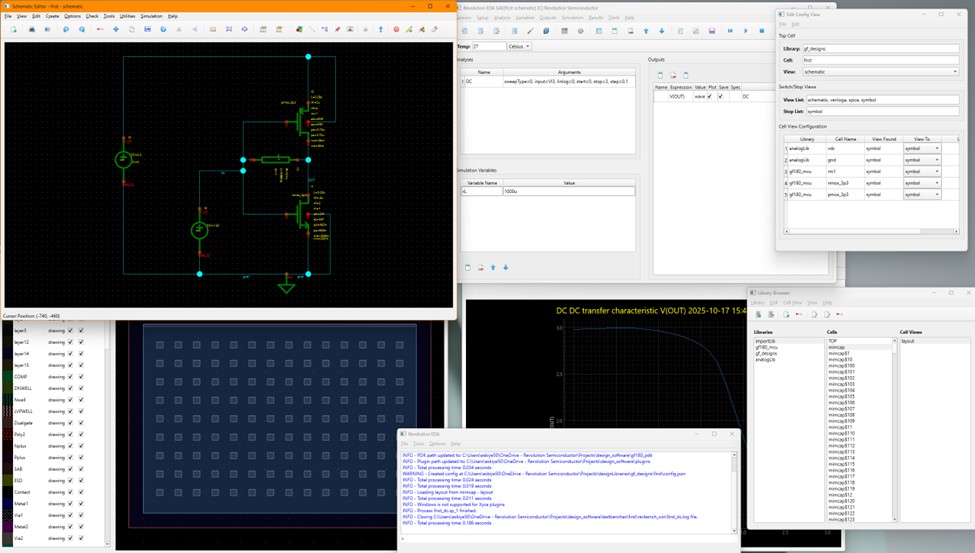

Revolution EDA: A New EDA Mindset for a New EraMurat Eskiyerli, PhD, is the founder of Revolution…Read More

Revolution EDA: A New EDA Mindset for a New EraMurat Eskiyerli, PhD, is the founder of Revolution…Read More WEBINAR: Revolutionizing Electrical Verification in IC DesignIn the complex world of IC design, electrical…Read More

WEBINAR: Revolutionizing Electrical Verification in IC DesignIn the complex world of IC design, electrical…Read More Silicon Catalyst on the Road to $1 Trillion IndustryThere were quite a few announcements at the…Read More

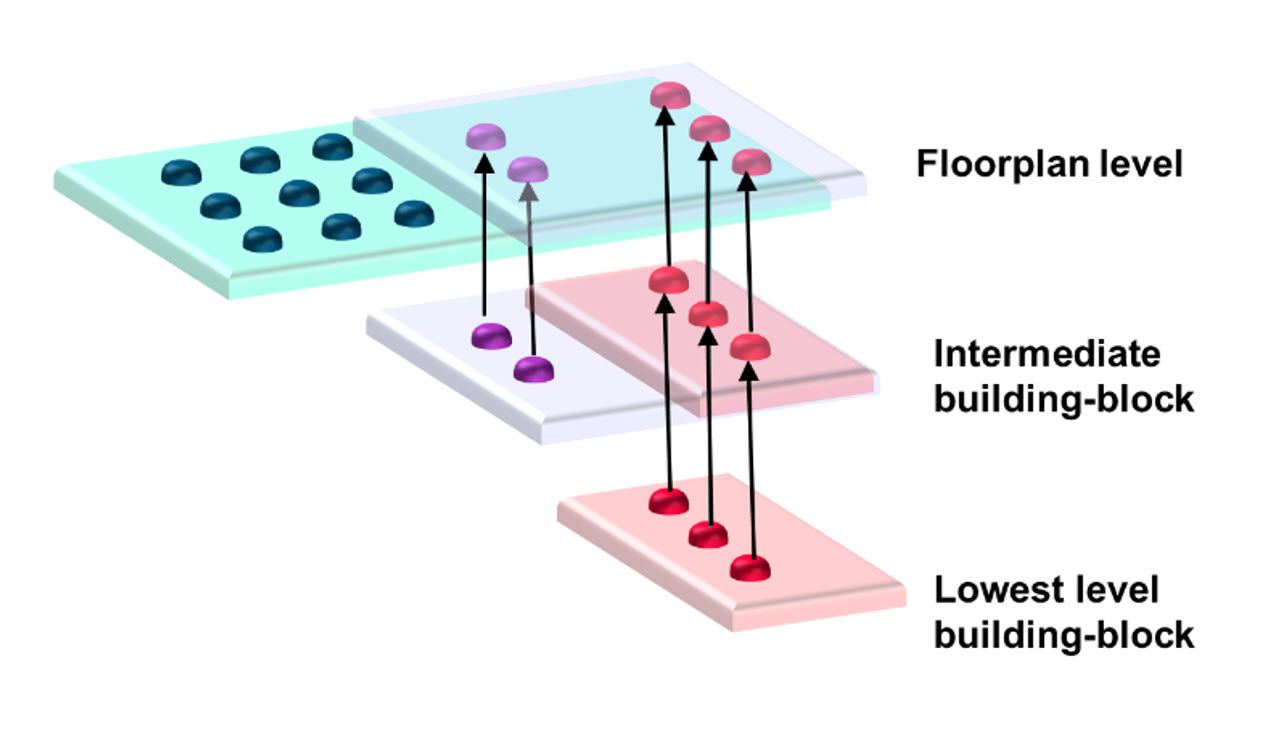

Silicon Catalyst on the Road to $1 Trillion IndustryThere were quite a few announcements at the…Read More Hierarchically defining bump and pin regions overcomes 3D IC complexityBy Todd Burkholder and Per Viklund, Siemens EDA…Read More

Hierarchically defining bump and pin regions overcomes 3D IC complexityBy Todd Burkholder and Per Viklund, Siemens EDA…Read MoreSoftware Developers Turn to CacheQ for Multi-Threading CPU Acceleration

Three-year old CacheQ, founded by two former Xilinx executives and a clever group of engineers, produces a distributed heterogenous compute development environment targeting software developers with limited knowledge of hardware architecture.

The promise of compiler tools for heterogeneous compute systems intrigued… Read More

RealTime Digital DRC Can Save Time Close to Tapeout

Over the years DRC tools have done an admirable job of keeping pace with the huge growth of IC design size. Yet, DRC runs for sign off on the full design using foundry rule decks take many hours to complete. These long run times are acceptable for final sign off, but there are many situations where DRC results are needed quickly when small… Read More

Chips for America Act – Funding Failures & Foreigners or Saving Semiconductors?

-A repeat of the auto industry bailout of self inflicted issues?

-Not just money but systemic change is needed

-Perhaps chips need an Elon led revolution like autos & space

-Govt $ need focus not thrown into existing spend avalanche.

Are chips a replay of the auto industry bailout a decade ago? Deja Vu all over again.

The… Read More

Podcast Episode 23: What are chiplets and why are they gaining popularity?

Dan is joined by Krishna Settaluri, Co founder and CEO of Blue Cheetah. Krishna received his Ph.D. in electrical engineering from UC Berkeley and masters and bachelors from MIT specializing in design automation of high-speed silicon photonic links using analog generator technology. Krishna has worked at Apple, Google, Caltech… Read More

CEO Interview: Prakash Murthy of Atonarp

Prakash Murthy is the co-founder & CEO of Atonarp, a leading molecular diagnostics company HQ in Tokyo Japan. Murthy has two decades of experience in engineering management and entrepreneurial ventures. Murthy also co-founded Inspiration Technologies and C2Silicon Software and served as the CEO of Core Solutions Inc.… Read More

Speed Up LEF Generation Times on Huge IC Designs

For IC designs there are many data formats used throughout the logical and physical design process, and one of those file formats is called LEF, an acronym for Library Exchange Format, created by Tangent, an early EDA company with Place and Route tools that was acquired by Cadence way back in March 1989. LEF generation times can become… Read More

Analog Sensing Now Essential for Boosting SOC Performance

In today’s System-on-Chip (SOC), analog blocks are used in many places such as I/O cells for communication, PLLs for generating clocks, LDO’s for converting supply voltage to internal rail voltage, Sensors for qualifying external characteristics such as temperature, light, motion, etc. However new advanced designs now require… Read More

Cadence adds a new Fast SPICE Circuit Simulator

In the early years of Cadence their growth was bolstered through many well-timed acquisitions, however over the last several years I’ve noticed a distinctively different trend where they have internally developed EDA tools. I had a Zoom call with Jay Madiraju from Cadence, who markets their newly announced Fast SPICE … Read More

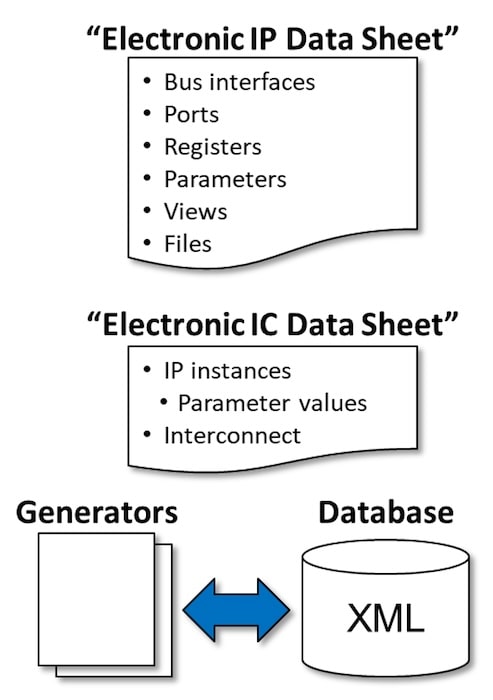

IP-XACT Resurgence, Design Enterprise Catching Up

This standard has been around in one form or another for over ten years and was then arguably ahead of its time. RTL designers were confused: ‘We already have RTL. Why do we need something else?’ I also didn’t get it. Still, the standard plugged ahead among the faithful and found traction among IP vendors. Particularly as a common format… Read More

An Insight into Building Quantum Computers