Artificial intelligence (AI) is a term used to describe machines that can perform tasks that normally require human intelligence, such as visual perception, speech recognition, decision-making, and language translation. AI is classified into three main types: Narrow AI, General AI, and Super AI. Each type of AI has its unique… Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More

Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read MoreIntel Keynote on Formal a Mind-Stretcher

Synopsys has posted on the SolvNet site a fascinating talk given by Dr. Theo Drane of Intel Graphics. The topic is datapath equivalency checking. Might sound like just another Synopsys VC Formal DPV endorsement but you should watch it anyway. This is a mind-expanding discussion on the uses of and considerations in formal which … Read More

eFPGA goes back to basics for low-power programmable logic

When you think “FPGA,” what comes to mind? Massive, expensive parts capable of holding a lot of logic but also consuming a lot of power. Reconfigurable platforms that can swallow RTL for an SoC design in pre-silicon testing. Big splashy corporate acquisitions where investors made tons of money. Exotic 3D packaging and advanced… Read More

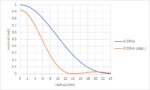

Lithography Resolution Limits: The Point Spread Function

The point spread function is the basic metric defining the resolution of an optical system [1]. A focused spot will have a diameter defined by the Airy disk [2], which is itself a part of the diffraction pattern, based on a Bessel function of the 1st kind and 1st order J1(x), with x being a normalized coordinate defined by pi*radius/(0.5… Read More

Checklist to Ensure Silicon Interposers Don’t Kill Your Design

Traditional methods of chip design and packaging are running out of steam to fulfill growing demands for lower power, faster data rates, and higher integration density. Designers across many industries – like 5G, AI/ML, autonomous vehicles, and high-performance computing – are striving to adopt 3D semiconductor… Read More

Samtec Lights Up MemCon

Every conference and trade show that Samtec attends is better for the experience. Samtec has a way of bringing exciting and innovative demos and technical presentations to any event they attend. I personally have fond memories of exhibiting next to Samtec at an early AI Hardware Summit at the Computer History Museum in Mountain… Read More

Podcast EP148: The Synopsys View of High-Performance Communication and the Role of Chiplets

Dan is joined by John Swanson, who is the HPC Controller & Datapath Product Line Manager in the Synopsys Solutions Group. John has worked in the development and deployment of verification, integration, and implementation tools, IP, standards, and methodologies used in IP-based design for over 25 years at Synopsys.

Dan explores… Read More

CTO Interview: Dr. Zakir Hussain Syed of Infinisim

Zakir Hussain is a co-founder of Infinisim and brings over 25 years of experience in the Electronic Design Automation industry. He was at Simplex Solutions, Inc. (acquired by Cadence) at its inception in 1995 through the end of 2000. He has published numerous papers on verification and simulation and has presented at many industry… Read More

Must-attend webinar event: How better collaboration can improve your yield

In today’s rapidly evolving semiconductor industry, the demand for high-quality and reliable semiconductors at a reasonable cost is increasing. This is why world-class yield management has become more and more important for fabless semiconductor companies and IDMs.

Accellera Update at DVCon 2023

I have a new-found respect for Lu Dai. He is a senior director of engineering at Qualcomm, with valuable insight into the ground realities of verification in a big semiconductor company. He is on the board of directors at RISC-V International and is chairman of the board of directors at Accellera, both giving him a top-down view of… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry