The rapid rise of artificial intelligence is fundamentally reshaping computing architectures. As AI models scale toward trillions of parameters, traditional approaches to performance improvement are no longer sufficient. Instead, the industry is entering a new era where system-level innovation, advanced packaging, … Read More

Two Paths for AI in Semiconductor Manufacturing: Platform Integration vs. Point Solutions Semiconductor manufacturing has become one of the…Read More

Two Paths for AI in Semiconductor Manufacturing: Platform Integration vs. Point Solutions Semiconductor manufacturing has become one of the…Read More Carbon in the Age of AI Chips: What the Semiconductor Industry Needs to Know This Earth DayStephen Russell: Senior Technical Fellow, TechInsights Every April,…Read More

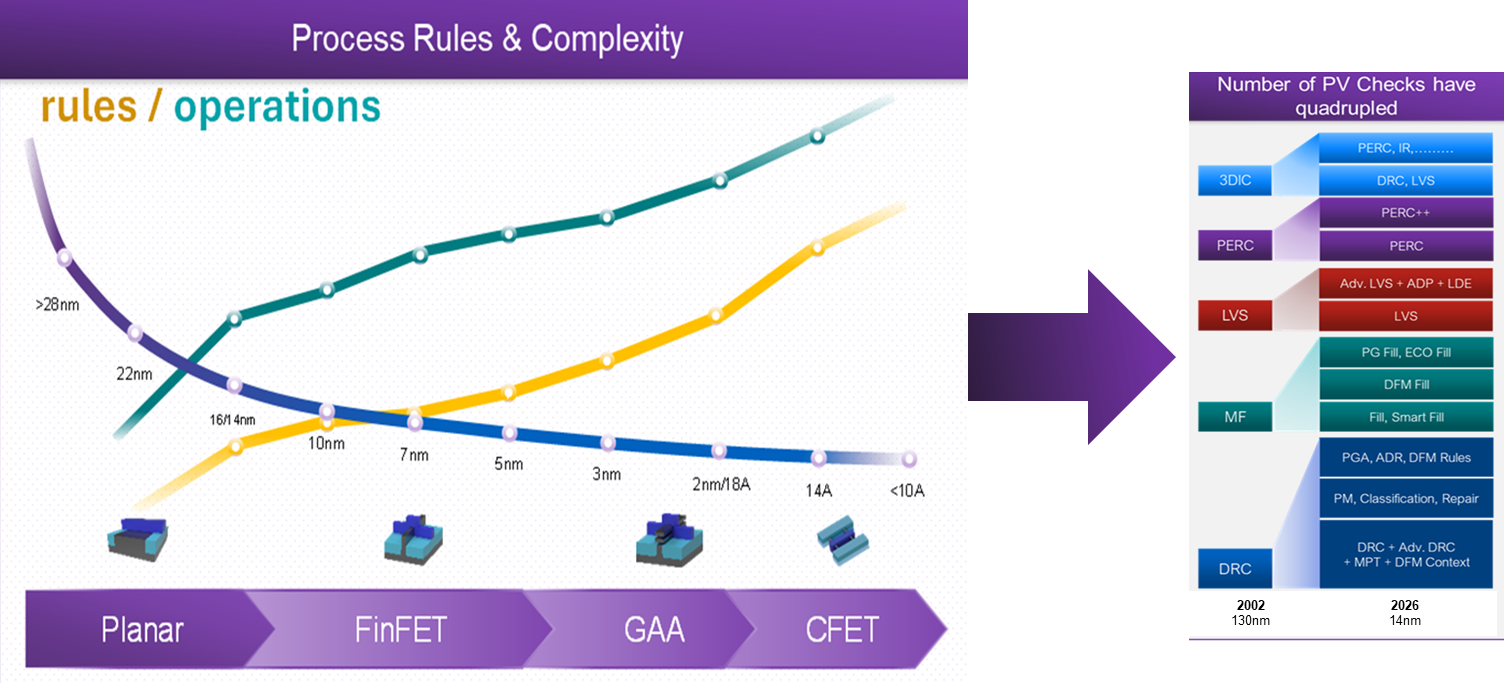

Carbon in the Age of AI Chips: What the Semiconductor Industry Needs to Know This Earth DayStephen Russell: Senior Technical Fellow, TechInsights Every April,…Read More How to Overcome the Advanced Node Physical Verification BottleneckIt is well-known that advanced semiconductor process technology…Read More

How to Overcome the Advanced Node Physical Verification BottleneckIt is well-known that advanced semiconductor process technology…Read MoreWAVE-N Specialized Video Processing NPU for Edge AI Systems

The rapid growth of AI applications in edge devices has created a strong demand for specialized hardware capable of performing high-performance neural network inference under strict power and latency constraints. Traditional CPUs and GPUs often struggle to meet the efficiency requirements of embedded and mobile systems.… Read More

Complex PCB signoff challenges

Many complex PCB designs have high data-rate signals like USB, PCIe, DDR and HDMI which call for more thorough verification methods to ensure compliance plus mitigate any signal integrity, power integrity and EMI/EMC issues. Siemens has a methodology that uses automated rule-based electrical verification with an EDA tool,… Read More

Dr. Cliff Hou and the TSMC N2 Process Technology

Before assuming his current position, Dr. Hou held several key leadership roles. He served as Vice President of Design and Technology Platform from 2011 to 2018, and later as Vice President of Technology Development starting in August 2018. Earlier in his career, from 1997 to 2007, he established TSMC’s technology design kit

UX in Agentic Systems. Innovation in Verification

A switch this month to principles behind building effective agentic systems, going beyond simply a new way to stitch together tools, agents and orchestration, to deeper consideration of user experience and how we most effectively blend agentic with human-in-the-loop. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano… Read More

Scalable Network-on-Chip Enables a Modular Chiplet Platform

The semiconductor industry is undergoing a profound transformation as system complexity, performance expectations, and time-to-market pressures continue to rise. Traditional monolithic system-on-chip (SoC) designs are increasingly giving way to modular, chiplet-based architectures that enable flexibility, scalability,… Read More

The Shift to System-Level AI Drives Next-Generation Silicon

At its 2026 Technology Symposium, TSMC delivered a clear message: the AI era has entered a new phase. The primary constraint is no longer model capability, but the systems required to run those models at scale. Addressing this shift will demand significant advances in semiconductor technology, spanning compute, memory, interconnects,… Read More

All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single Die

The rapid evolution of wireless audio has placed unprecedented demands on system integration, power efficiency, and performance. Against this backdrop, the webinar “All-in-One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single Die” offers a timely and technically rich exploration of how modern semiconductor design… Read More

Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet Governance

By Dr. Moh Kolbehdari

Dr. Moh Kolbehdari is a Senior Lead Architect at Socionext, where he specializes in the industrialization of high-performance AI chiplets and 1.8-Tb/s interconnects. With over two decades of experience in SI/PI, electromagnetic field theory, and system-level architecture, he has been a pivotal force… Read More

SemiWiki Q&A with Julie Rogers, Executive Director, ESD Alliance

The Electronic System Design Alliance (ESD Alliance), a SEMI Technology Community, an international association of companies providing goods and services throughout the semiconductor design ecosystem, is a forum to address technical, marketing, economic and legislative issues affecting the entire industry. It acts … Read More

Is Intel About to Take Flight?