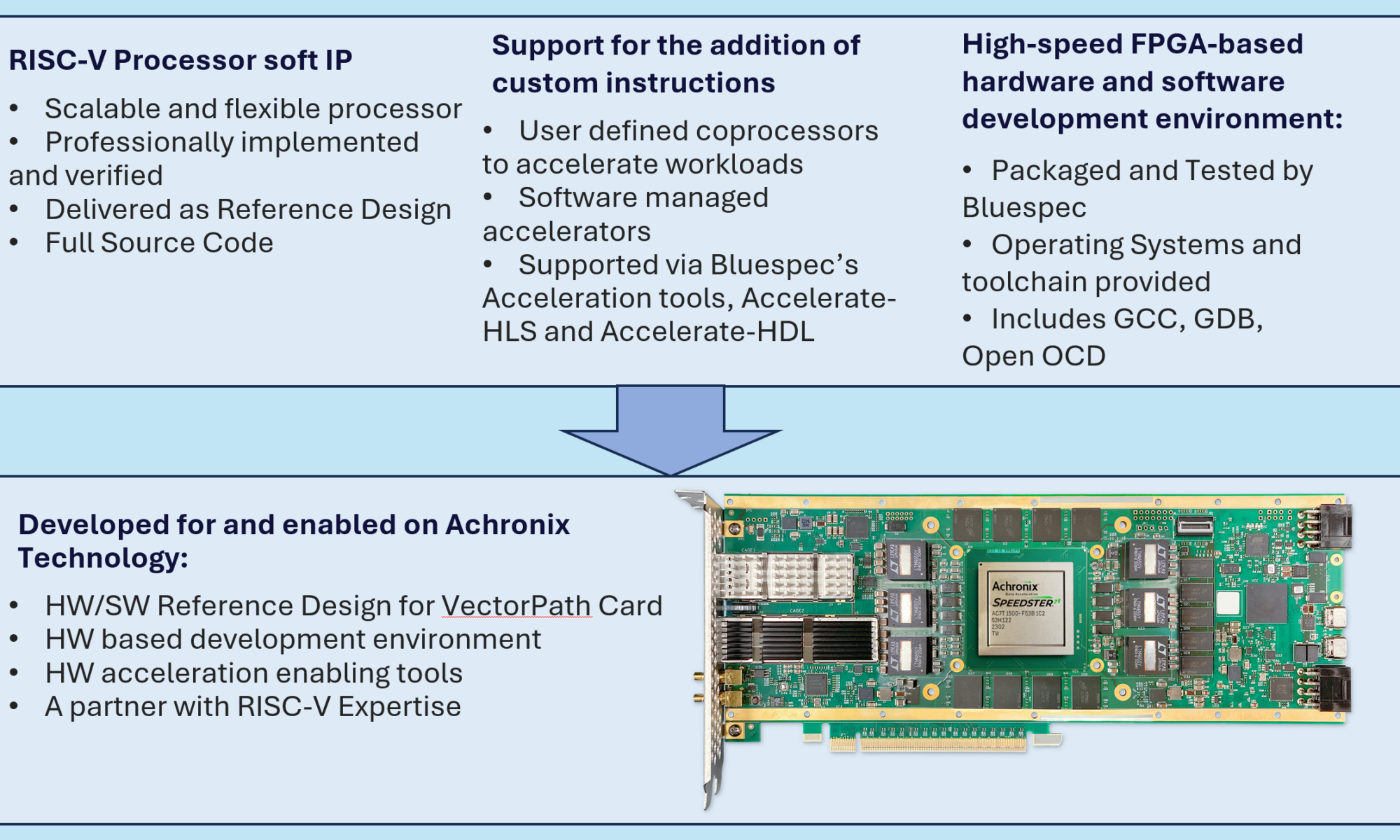

Recently, a partnership between Achronix and Bluespec has been in the news. Bluespec RISC-V processors are available as soft cores in a Speedster®7t FPGA on Achronix’s VectorPath® PCIe development card or in a standalone Speedster7t FPGA. We spoke with executives from Achronix and Bluespec about the impetus for this effort and where it might lead. Industry veterans Nick Ilyadis, VP of Product Planning at Achronix (NI), and Loren Hobbs, VP of Product and Business Development at Bluespec (LH), shared their thoughts.

SW: What brought Achronix and Bluespec together for this partnership?

NI: Several years ago, we searched for a small processor core we could use in our FPGAs to do maintenance, train memory interfaces, and perform other tasks. We found Bluespec had a nice, compact core that would meet our needs, and we licensed it and started working with it. In the process, I became aware of other Bluespec capabilities and the breadth of their CPU core offerings, particularly the ability to create custom instructions for accelerators coupled to cores. There was a natural fit in having a CPU use the FPGA fabric for acceleration in a very tightly coupled manner. Using our 2D network-on-chip (NoC) as a transport mechanism for RISC-V cores, accelerators, memory resources, and PCIe differentiates our solution.

SW: Was it all about the 2D NoC, or were there other Speedster7t FPGA attributes that made this attractive for Bluespec?

LH: We agree – this partnership has been in the making for years and is not just a recent discovery, starting with our MCU core and adding from there. We saw an FPGA with a combination of high-speed memory interfaces, high-speed I/O devices, and high bandwidth across the FPGA fabric with the 2D NoC. There was also the idea of scalable processing with one or more instances of our RISC-V processor cores working with accelerators in a design. The architecture fits together nicely.

SW: Can you describe, maybe by a range, how much of the Speedster7t FPGA area a Bluespec RISC-V core takes?

LH: It’s a range since we have smaller and larger RISC-V cores, and it varies by features included and how much customization is involved. Off the top of my head, a small core would be somewhere from 2 to 4% of the device. On larger cores, with floating point and instruction extensions, we’d be perhaps 8 to 9% of the device. Less than 10% of a device for one core is a good starting point.

SW: Aside from customization capability, how does a Bluespec RISC-V core differ from other RISC-V offerings?

LH: We follow the RISC-V spec closely, including for instruction extensions. High-end processing isn’t our target – we’re more about doing small routines and managing accelerators and I/O, running on bare metal, or using an RTOS such as FreeRTOS, or Linux. We offer a five-stage pipeline and a choice of instruction extensions beyond the basic integer instructions, with options for multiplication (M), atomic (A), and compressed (C) instructions. We also support optional single or double-precision floating-point instructions (F and D). Our key differentiator is tooling to quickly add support for accelerators as custom instructions in a core.

SW: We’ve talked with Achronix before about Speedster7t FPGA applications like automated voice recognition (AVR) and the evolution of SmartNICs into data processing units (DPUs). How do you see RISC-V cores meshing with other IP in an FPGA?

NI: One example is AI/ML inferencing. Neural networks now have tens of thousands of nodes with tens of thousands of interconnects. They are getting so large that they are outgrowing a static implementation in a single FPGA, so the strategy is now breaking up the network into layers and segments, then dynamically loading individual segments, activation functions, and intermediate values. Accelerators can do matrix calculations, sigmoid functions, normalization, or quantization. Subsystems can be spread across the device and connected by our 2D NoC. A RISC-V core orchestrates, firing off a sophisticated state machine initiating accelerators on demand, and high timing accuracy is crucial. Signal processing chains are another example, with DSP blocks and FIR filters for wireless radios including 5G/6G. DPUs also need a processor to handle control plane versus data plane traffic. We’ve even talked to customers about using AI/ML in a DPU to learn how a normal network runs and adjusts when abnormalities appear.

SW: How is the solution delivered to customers?

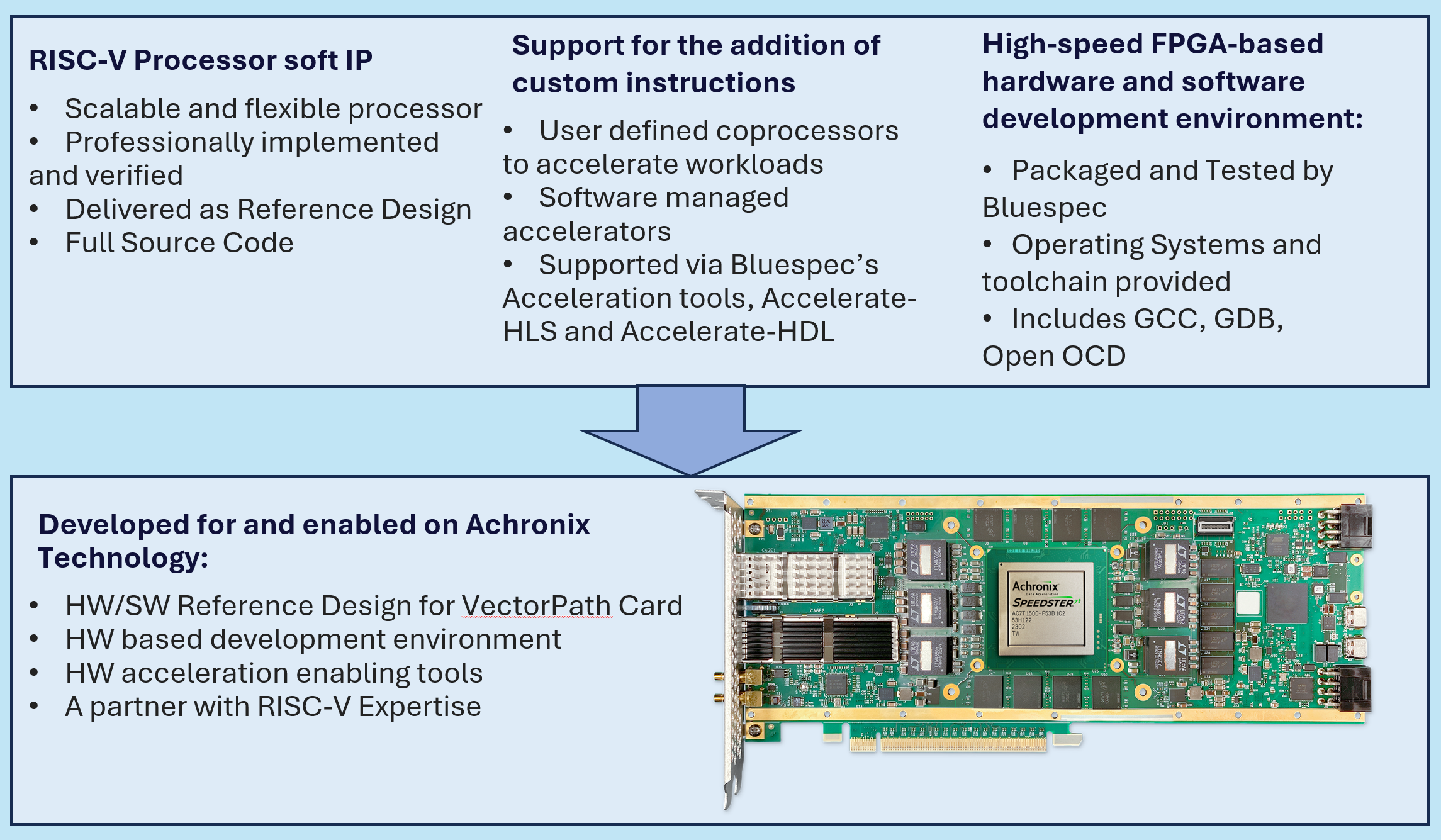

LH: We provide the RISC-V cores as soft IP in Verilog, and we also provide the open-source toolchains. We include a reference design for initializing the core in software, and we can add a ready-to-run embedded operating system. We also have tooling for developing custom instructions and a software layer for managing accelerators, and it works with high-level synthesis tools or Verilog – it takes most of the hard work out of adding accelerator blocks. Bluespec works closely with our customers, providing “white glove” assistance to bring up the solution. We’ll deliver directly to a customer and help them along the way.

NI: Bluespec has made it easy to load their RISC-V cores onto our VectorPath development card over PCIe as a bitstream. A core can use memory blocks in the Speedster7t FPGA for cache and externally attached memory on the VectorPath card for storing data structures. We’re moving a demo for Bluespec cores on a VectorPath card into our Achronix Virtual Lab (AVL) so customers can access it in the cloud through a VPN to try it out.

SW: What does the ideal customer for this look like?

NI: We’re looking for large telecom infrastructure providers, a networking company, or companies developing AI/ML inference solutions. We’d also like to engage with hyperscalers, especially ones that might have supply chain problems with GPU-based solutions.

LH: We’re in line with that list of traditional customers. We often see larger customers start small, with one team using the design and finding the value, and then it spreads to other teams in the organization. Many of our opportunities come from cross-organizational references.

SW: Is there still some hesitation over the perceived difficulty of programming FPGAs?

NI: Our bitstream loading is simple – we can load from a flash drive, over PCIe, or soon over Ethernet. If a user has software running on a server, our tools help them embed the bitstream inside their operational code and load it. We’re trying to make it as frictionless as possible. With 15 years of tool development under our belt, our code is mature.

LH: Bringing more developers into FPGAs is an age-old question. A top-down architectural understanding of NoCs and interconnected blocks helps, but our combined tools take care of the bottom-up details of programming the FPGA so users can take advantage of the technology.

SW: Finally, where do you see the technology heading?

NI: We’re working on a couple of things – a “baby brother” of the Speedster7t that could still hold small RISC-V cores, and a hardened RISC-V core outside of the fabric so resources are fully available to customers.

LH: Hardening cores enables higher performance, for sure. We also think multicore opportunities will emerge when customers start seeing the possibilities. We’ll continue to align roadmaps and tailor implementations that fit well together.

For more information on Bluespec RISC-V soft cores in Achronix FPGAs:

RISC-V Processors for Achronix FPGAs

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.