Recently, a partnership between Achronix and Bluespec has been in the news. Bluespec RISC-V processors are available as soft cores in a Speedster®7t FPGA on Achronix’s VectorPath® PCIe development card or in a standalone Speedster7t FPGA. We spoke with executives from Achronix and Bluespec about the impetus for this effort … Read More

Tag: 2D NoC

Scaling LLMs with FPGA acceleration for generative AI

Large language model (LLM) processing dominates many AI discussions today. The broad, rapid adoption of any application often brings an urgent need for scalability. GPU devotees are discovering that where one GPU may execute an LLM well, interconnecting many GPUs often doesn’t scale as hoped since latency starts piling up with… Read More

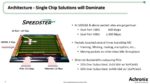

Integrated 2D NoC vs a Soft Implemented 2D NoC

We are living in the age of big data and the future is going to be even more data centric. Today’s major market drivers all have one thing in common: efficient management of data. Whether it is 5G, hyperscale computing, artificial intelligence, autonomous vehicles, or IoT, there is data creation, processing, transmission, and … Read More

2D NoC Based FPGAs Valuable for SmartNIC Implementation

Smart network interface cards (SmartNICs) have proven themselves valuable in improving network efficiency. According to Scott Schweitzer, senior product manager at Achronix, it has been shown that SmartNICs can relieve up to – and perhaps beyond – 30% of the host processor’s loading. SmartNICs started out taking… Read More

PCIe Gen5 Interface Demo Running on a Speedster7t FPGA

The major market drivers of today all have one thing in common and that is the efficient management of data. Whether it is 5G, hyperscale computing, artificial intelligence, autonomous vehicles or IoT, there is data creation, processing, transmission and storage. All of these aspects of data management need to happen very fast.… Read More

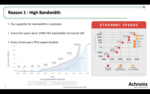

Five Reasons Why a High Performance Reconfigurable SmartNIC Demands a 2D NoC

As part of their webinar series, SemiWiki hosted one in June with the title “Five Reasons Why a High Performance Reconfigurable SmartNIC Demands a 2D NoC.” The talk by given by Scott Schweitzer, Sr. Manager, Product Planning at Achronix. Scott is a lifelong technology evangelist and focuses on recognizing technology trends and… Read More

Take the Achronix Speedster7t FPGA for a Test Drive in the Lab

Achronix is known for its high-performance FPGA solutions. In this post, I’ll explore the Speedster7T FPGA. This FPGA family is optimized for high-bandwidth workloads and eliminates performance bottlenecks with an innovative architecture. Built on TSMC’s 7nm FinFET process, the family delivers ASIC-level performance … Read More

WEBINAR: 5 Reasons Why a High Performance Reconfigurable SmartNIC Demands a 2D NoC

If you are involved in designing systems that process data, you’re going to want to attend this webinar. Practically speaking, this should include a large percentage of the SemiWiki readership. Since data is the new oil there are a lot of applications drawn to data and information processing. Before we explore this webinar, let’s… Read More