With growing SoC size, complexity, software and hardware content in it and shrinking time-to-market, the SoC design completion in time has become increasingly dependent on IP which need to be sourced (internally or externally), customized according to the design need and integrated together into the SoC. While IP providers can provide best optimized IP with good configurability and flexibility, its integration into SoC is not a straight forward task; it needs significant amount of work to consider various configurations, negotiate with significant amount of legacy design, adhere to frequent changes in standards and protocols, optimize, prototype and validate it in an SoC context before its integration into the SoC. How to do it when the final SoC is not yet available?

That’s the beauty of EDA vendors getting into the shoes of IP providers to provide complete automation to make an IP ready to be integrated into an SoC as fast as possible. While Synopsys, over a couple of years, has built a strong IP portfolio, it is now marching into accelerating the IP integration into SoC through several of its programs under “IP Accelerated Initiative”. Synopsys is providing DesignWareIP Prototyping Kits for several IP titles to accelerate designers’ IP prototyping, software development, and integration into SoCs. A Kit specific to an IP comes with proven reference design that can be used to explore design trade-offs with specific configurations of the IP, optimize the IP and validate it with fast iterative flow. The same design can be set as a target for early software bring-up, debug and test.

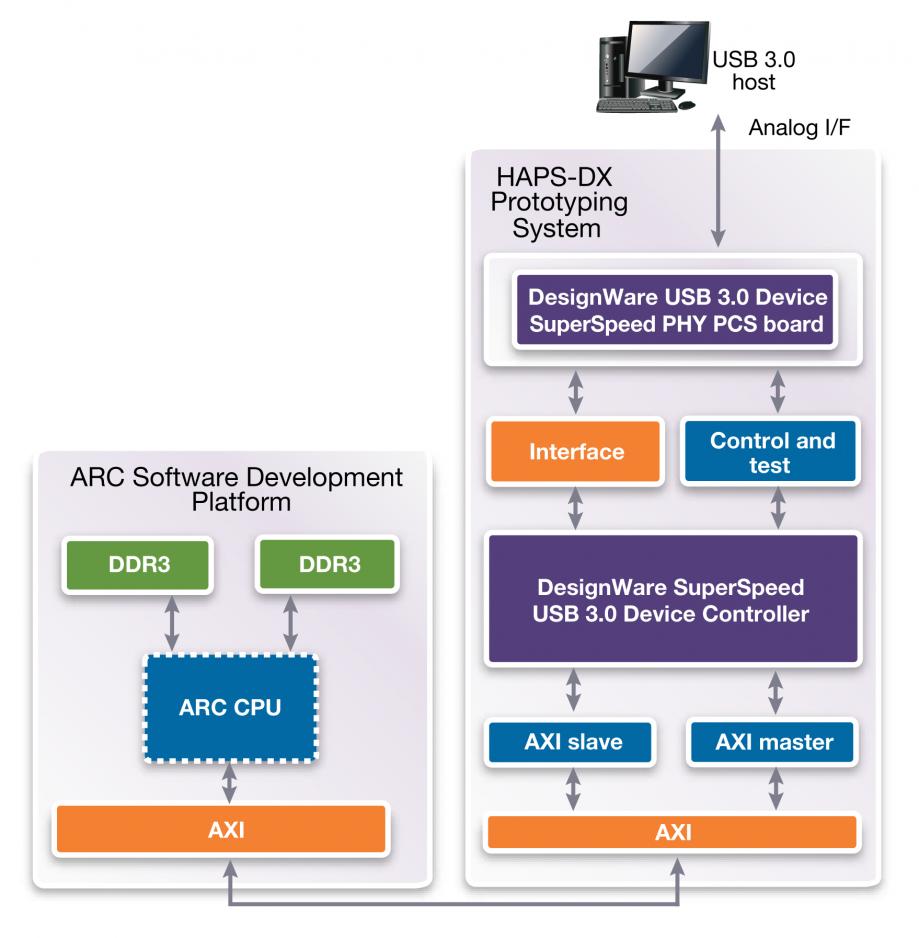

Above is an IP Prototyping Kit for USB 3.0 Device Controller. The Kits, in general, include Synopsys’ HAPS-DX FPGA based prototyping system with proven reference design, pre-configured IP, necessary SoC integration logic, PHY daughter board, simulation testbench, reference drivers and application examples along with either a connection to host PC (running the target OS) or DesignWare ARC processor based 32-bit software development platform running Linux. Assisted with Synopsys’ coreConsultantIP configuration tool, ProtoCompiler DX development and debug tool, and several scripts, designers can instantly modify and optimize the IP configuration, develop drivers and other software and accelerate integration of the IP into the target SoC.

The USB 3.0 Kit has been observed to be working excellently in customer’s design environment. It accelerates driver and software development early for customers to advance their schedule for FPGA validation by several weeks.

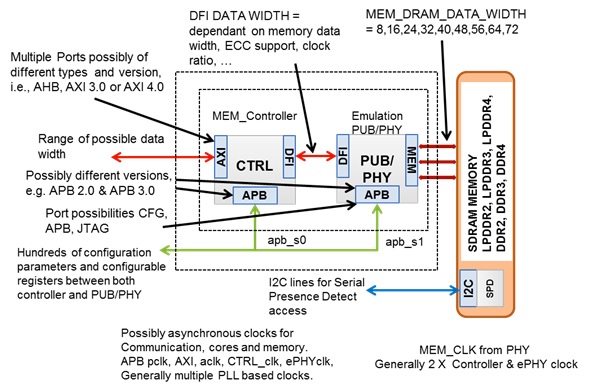

There is an example of a DDR IP Subsystem consisting of memory controller, communication ports, PHY block and so on, each of which requires configuration at hardware and software levels to ultimately define permissible functionality, range of registers, and connectivity characteristics and so on. While an FPGA image rebuild or even simulation (that involves OS setup, loading, initialization, accessing proper communication busses and debugging) for any hardware change can take several hours to days, the IP Prototyping Kit can accelerate iteration cycles by providing IP reference designs in a tested environment that allows fast exploration of different configurations through hardware-aware development tools. Look herefor more details on the Kit for “DDR uMCTL2 and Gen2 multiPHY with ARC Software Development Platform”.

Today, Synopsys provides DesignWare IP Prototyping Kits for multiple interface protocols including USB 3.0, SSIC, PCI Express 3.0 and 2.0, DDR3, LPDDR3, LPDDR2, MIPI CSI-2, HDMI 2.0, and JEDEC UFS. Through these Kits, the designers need not spend much time in learning about the internals of IP and other details. A Kit provides ready environment for designers to implement an IP in an SoC context instantly, thus boosting their productivity which helps them in meeting challenging time-to-market.

More Articles by Pawan Fangaria…..

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.