When USB initially came out it revolutionized how peripherals connect to host systems. We all remember when Apple did away with many separate connections for mouse, keyboard, audio and more with their first computers supporting USB. USB has continued to develop more flexibility and more throughput. In 2015 Apple again introduced the MacBook with just a single USB Type C connector and only a headphone jack. The Type C connector has been used for USB 3.2, but will now also be used for the latest USB specification – USB4. Synopsys recently gave an excellent presentation on USB4 and their DesignWare USB4 PHY IP at The TSMC OIP event. Despite all the changes and improvements in USB, each generation maintains compatibility with earlier versions. Gervais Fong, Director of Marketing at Synopsys, clearly described how backwards compatibility is maintained while impressive new features and performance are added.

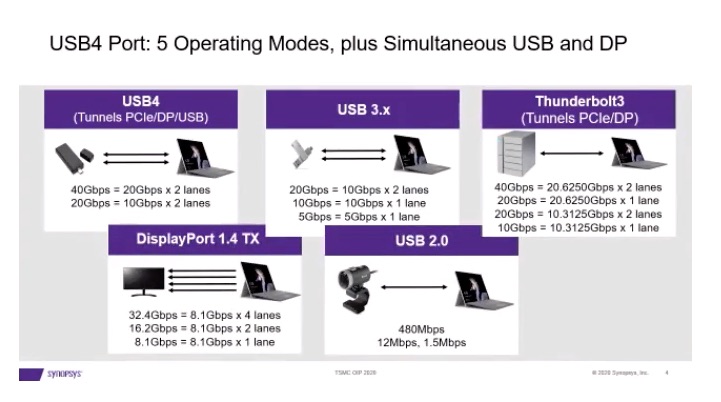

In 1998 the first specification for USB 1.1 allowed data transfers of 1.5 or 12 Mbits/s. Leaping forward, USB4 supports all previous data rates and can run at 40 Gbits/s max aggregate bandwidth. One of the biggest additions are the USB4 host controller and device routers. Nevertheless, USB4 maintains bypasses for 1 and 2 lane legacy USB up to 20Gbits/s and 1, 2 or 4 lanes for DisplayPort 1.4 TX up to 20 Gbits/s. This permits older devices that do not use a USB router to still transfer data. USB4 also supports tunneling of PCIe, USB and DisplayPort at up to 40 Gbits/s. USB4 incorporates UMTI+ and PIPE5.

Gervais included a useful slide showing USB4’s five different operating modes. Rather than try to describe the five modes, the slide is included below. The trend of combining protocols is significant. It means that with a single connector high speed data for peripherals, networking, storage and displays are all supported. This improves the user experience and offers unmatched flexibility. A high level of interoperability is available because Apple and Intel are both contributing and supporting USB’s evolution.

While the user experience is improving, chip designers who want to incorporate USB4 need to ensure that their USB silicon is fully compliant and has been completely verified. The USB4 PHY alone needs to support a dizzying array of operating modes, configurations, protocols and speeds. Gervais points out the USB4 PHY is not just handling USB, it is handing DisplayPort and Thunderbolt as well. The PHY has to interface with and be compatible with the router and controllers.

Synopsys has developed a DesignWare USB4 PHY that meets all of the specification’s requirement and is available on 12nm, 6/7nm and 5nm. It is built on an optimized, low power SerDes. Gervais said that they have over 100,000 CPU hours of simulation with Synopsys routers and controllers.

Gervais also talked about their test silicon from TSMC N5 that is now being tested. The PHY includes a programmable 3-tap Feed Forward Equalizer that is used to adjust the equalization for the various operating modes and frequencies. This is essential for meeting the USB4 PHY specifications. They have achieved first silicon success in TSMC N5P. The eye diagram for this silicon at 20 Gbits/s shows a wide open eye for TX. The receive path includes a Continuous Time Linear Equalizer and 1-tap Decision Feedback Equalizer with programmable settings.

The complete DesignWare USB4 solution from Synopsys includes PHYs, router, controller, verification IP and supporting subsystems. The talk presented a comprehensive overview of USB4 and its requirements, as well as an insightful look at the Synopsys DesignWare that supports interface development.

Also Read:

AI/ML SoCs Get a Boost from Synopsys IP on TSMC’s 7nm and 5nm

Parallel-Based PHY IP for Die-to-Die Connectivity

Making Full Memory IP Robust During Design

Share this post via:

Comments

2 Replies to “Synopsys talks about their DesignWare USB4 PHY at TSMC’s OIP”

You must register or log in to view/post comments.