In a fantasy world where there were no coding errors or integration issues, FPGA designs would fly straight through synthesis easily and quickly. Maybe that world does exist somewhere. For the rest of us, who have experienced the agony of running a large FPGA design – again – only to find another error and have to start over, there has to be a better way.

It gets even better when we start talking about pouring really large RTL designs, too big for even a single behemoth FPGA, into an FPGA prototyping system partitioned across multiple devices. Depending on how adroit the partitioner is, that process can go smoothly or it can make a complete mess. There’s no way of finding out until you think you’re done.

I get hundreds of press releases a month, and I’m naturally a bit on the cynical side when it comes to technology claims. Headline writing is an art unto itself. Normally, a new version of an existing product doesn’t rewrite the entire story and make it worth reading again. I had to take a hard look at the Synopsys release underneath this headline – “Latest Release of Synplify Software Cuts Days off Implementation Time” – before really understanding the significance.

Along with synthesis algorithm improvements continuing from earlier releases, the 2012.09 release of Synplify Premier adds hierarchical design error isolation and incremental fix, multiprocessor compilation, and continue-on-error capability, all going into their claim of reducing implementation time on two dimensions: speeding up the build process for the entire design, and reducing the number of subsequent iterations needed to fix a design. A quick look at these three capabilities:

Hierarchical capabilities: the idea is instead of building the entire design, “divide-and-conquer” a design into blocks which are self-contained, then merge any fixed blocks back into the main design without rebuilding the rest. This allows blocks to be worked on by different teams in parallel. By capturing design artifacts at the block level – TCL scripts, place-and-route flows, and other information – each block can be isolated for debug and modification.

Automated multiprocessing: if a design can be partitioned onto multiple target FPGAs in a prototyping platform, then it can certainly be partitioned across a multiprocessor design server for synthesis. Synopsys has added technology they call Automatic Compile Points, which splits the synthesis task across CPUs for a typical 30% time gain using two processors. (That is probably a conservative figure. The 10x improvement cited elsewhere takes into account every improvement from fast synthesis mode, better algorithms, and parallelism, and is likely very optimistic. Your experience will likely be significant, somewhere between those two figures.) This also works with manually-created RTL partitions, so FPGA prototyping engineers can leverage multiprocessor synthesis on their existing designs.

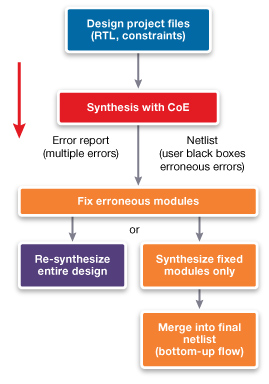

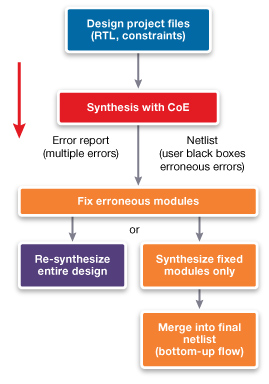

Continue-on-error:This alone can be a lifesaver for the FPGA prototyping team that has to deal with a mashup of RTL code they are likely unfamiliar with and trying to partition. That mess I referred to earlier can be hundreds of errors from thousands of design files in an initial synthesis. Synplify Premier can create a consolidated report of errors with problem modules highlighted, and allow modules to be fixed, resynthesized, and incrementally merged back into the final netlist.

There’s a lot more to the fast turnaround story of Synplify, including a white paper. There are also a few other unique features to the 2012.08 release, with unique support for Xilinx Vivado Design Suite, triple modular redundancy in Altera devices, and support for the relatively new Achronix Speedster22i family, but we’ll save those for another time.

Are you using Synplify tools and have a story to share? How do these improvements sound compared to your experience in the FPGA synthesis cycle using other tools? Are there other significant FPGA synthesis problems that need attention from tools vendors? Thoughts welcome.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.