I earlier wrote a piece to make you aware of a webinar to be hosted by Aldec on some of their capabilities for partitioning large designs for prototyping. That webinar has now been broadcast and I have provided a link to the recorded version at the end of this piece. The webinar gets into the details of how exactly you would use the software… Read More

Tag: partitioning

Webinar: Aiding ASIC Design Partitioning for multi-FPGA Prototyping

The advantages of prototyping a hardware design on a FPGA platform are widely recognized, for software development, debug and regression in particular while the ultimate ASIC hardware is still in development. And if your design will fit into a single FPGA, this is not an especially challenging task (as long as you know your way … Read More

Safer SoCs for safer driving

Flip on the TV, and a car commercial is bound to pop up shortly touting one of two technological aspects. One is center stack integration of smartphone-style applications. The other is advanced driver assistance systems (ADAS) featuring cameras, radar, and other sensors helping cars … Read More

Second FPGA to the right, and straight on ‘til it works

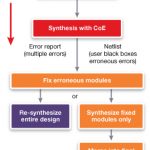

In a fantasy world where there were no coding errors or integration issues, FPGA designs would fly straight through synthesis easily and quickly. Maybe that world does exist somewhere. For the rest of us, who have experienced the agony of running a large FPGA design – again – only to find another error and have to start over, there … Read More

Partitioning Pavilion Panel

I don’t think it can be a surprise to anyone reading this that designs have been getting larger. Someone called Moore said something about it decades ago, or so I heard. Designs are so large that they need to be partitioned into smaller parts. The two main motivations for this are that some design tools, especially place &… Read More