I wrote recently about how virtual prototypes (in the form of VDKs) can help embedded software teams practice continuous integration. Synopsys has just released a white paper detailing a practical approach to building a VDK, using the Juno ARM development platform (ADP) to illustrate. Just as a reminder, the point of a virtual… Read More

Nvidia Drives into New Market with Deep Learning and the Drive PX 2

Nvidia has found that video games are the perfect metaphor for autonomous driving. To understand why this is so relevant you have to realize that the way self-driving cars see the world is through a virtual world created in real time inside the processors used for autonomous driving – very much like a video game. It’s a little bit like… Read More

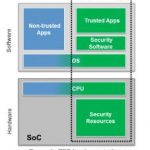

How to Secure a SoC while Keeping Area and Power Competitive?

I have attended LETI conference last June and remember the paper presented by Alain Merle, their security guru. Alain said that smart cards are secured because up to 50% of the Silicon area is dedicated to security. When you design a SoC to address applications like smart metering, NFC payment or embedded SIM, you know in advance … Read More

ATPG, Automotive and 7nm FinFET

The state of Texas hosted two or our industry’s big technical conferences and trade shows this year: DAC and ITC (International Test Conference). IC designers know about DAC in Austin, and test engineers know about ITC in Dallas. I travelled to Austin to cover DAC this past summer, and I was able to connect with Robert Ruiz … Read More

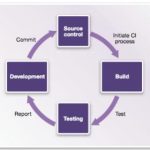

Embedded Agility

A familiar refrain in software development, as much as in hardware development, is that the size and complexity of projects continues to grow as schedules shrink and expectations of quality can increase dramatically. A common approach to managing this challenge in software programs is agile development practices and one aspect… Read More

Ford Motors Discusses Future Mobility Trends at Synopsys Seminar

Five or ten years ago it would have been hard to imagine someone from Ford Motors giving the keynote at a technology summit at a major EDA company like Synopsys. However, on November 2[SUP]nd[/SUP], Synopsys hosted a seminar on the topic of Automotive Architecture Design and System Testing, and Ford Technical Fellow Jim Buczkowski… Read More

FPGAs allow customization of SEU mitigation

Teams working on avionics, space-based electronics, weapons delivery systems, nuclear generating plants, medical imaging equipment, and other applications where radiation leads to single-event upsets (SEU) are already sensitive to functional safety requirements. What about automotive applications?

With electronic… Read More

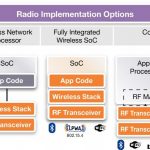

Why Integrate Bluetooth LE IP in a Single Wearable SoC?

Did you know that, in over 800 teardowns of mobile and wearable products from 2012 to 2015, wireless chips outnumbered the actual number of products, indicating multiple wireless ICs in some designs ([SUP]1[/SUP])? It could be interesting to look at the advantages of integrating wireless technology such as Bluetooth low energy… Read More

Circuit Simulation Videos Show How To

One of the things that I miss most about attending trade shows like DAC in the old days was that you actually got to see EDA tools being demonstrated live in the exhibit area. You could see what the GUI looked like, how the dialogs worked, and learn what kind of control you could have during analysis. Most of what you see today at DAC in the… Read More

Machine Learning – Turning Up the Sizzle in EDA

There’s always a lot of activity in EDA to innovate and refine specialized algorithms in functional modeling, implementation, verification and many other aspects of design automation. But when Google, Facebook, Amazon, IBM and Microsoft are pushing AI, deep learning, Big Data and cloud technologies, it can be hard not to see… Read More