You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 158

[name] => Foundries

[slug] => semiconductor-manufacturers

[term_group] => 0

[term_taxonomy_id] => 158

[taxonomy] => category

[description] =>

[parent] => 0

[count] => 1379

[filter] => raw

[cat_ID] => 158

[category_count] => 1379

[category_description] =>

[cat_name] => Foundries

[category_nicename] => semiconductor-manufacturers

[category_parent] => 0

[is_post] =>

)

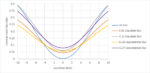

It has recently been revealed that the N5 node from TSMC has a minimum gate pitch of 51 nm [1,2] with a channel length as small as 6 nm [2]. Such a tight channel length entails tight CD control in the patterning process, well under 0.5 nm. What are the possible lithography scenarios?

Blur Limitations for EUV Exposure

A state-of-the-art

…

Read More

Recently TechInsights analyzed a Bitcoin Miner chip fabbed at SMIC and declared SMIC has a 7nm process. There has been some debate as to whether the SMIC process is really 7nm and what it means if it is 7nm. I wanted to discuss the case for and against the process being 7nm, and what I think it means.

First off, I want to say I am not going … Read More

The media has gone wild over a false report that Intel and TSMC are slowing down 3nm. It is all about sensationalism and getting clicks no matter what damage is done to the hardworking semiconductor people, companies and industry as a whole. And like lemmings jumping off a cliff, other less reputable media outlets perpetuated this… Read More

Pinpointing exactly when 450mm died is tricky. Intel’s pullback in 2014 has been cited as a pivotal moment because it was the main backer of the proposed transition, as it had been for the shift to 150mm (6-inch) wafers in the early 1980s.

However, the participation of global foundry leader TSMC was also seen as crucial if 450mm wafers… Read More

-Need more/less spend & more/fewer chips

-The irony of chips act passage & Intel stumble on same day

-Due to excess supply of chips, Intel cuts spending

-Due to shortage of chips, the government increases spending

-How did this happen on the same day? Cosmic Coincidence?

Timing is everything

The irony of intel cutting spending… Read More

Most people will be surprised by this but after working in Taiwan for many years I quite expected it. Intel Announced that MediaTek will use Intel Foundry Services for FinFET based smart edge device chips. MediaTek will start with Intel 16nm technology which originated from the legendary 22nm, the first commercial FinFET process.… Read More

At the recent VLSI Symposium on Technology and Circuits, Dr. Y.J. Mii, Senior Vice President of Research and Development at TSMC, gave a plenary talk entitled, “Semiconductor Innovations, from Device to System”. The presentation offered insights into TSMC’s future R&D initiatives, beyond the current roadmap. The associated… Read More

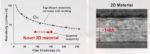

The VLSI Symposium on Technology and Circuits provides a deep dive on recent technical advances, as well as a view into the research efforts that will be transitioning to production in the near future. In a short course presentation at the Symposium, Marko Radosavljevic, from the Components Research group at Intel, provided … Read More

Intel announced today that they are partnering with cloud and EDA companies to better enable their foundry business. This is a natural extension of the Accelerator ecosystem program announced earlier. More and more chip designs are being done in the cloud and from my experience cloud based designs are better. Some companies use… Read More

TSMC recently held their annual Technology Symposium in Santa Clara, CA. The presentations provide a comprehensive overview of their technology status and upcoming roadmap, covering all facets of the process technology and advanced packaging development. This article will summarize the highlights of the advanced packaging… Read More

Solving the EDA tool fragmentation crisis