I talked to Dado Banatao today. He is managing partner at Tallwood Venture Capital today but back in the mid-1980s he was the founder of Chips and Technologies, the first fabless semiconductor company. The rumors that they had a hard time raising money because VCs couldn’t comprehend a fabless semiconductor company are … Read More

Electronic Design Automation

RealTime Register Retiming

I was at the EDAC CEO forecast meeting last week and one of the questions that was asked of EDAC members was “which is the hottest EDA startup?” The one with the most nominations was Oasys. So Oasys is hot.

But register retiming is hotter.

The latest announcement from Oasys this morning is that register retiming is now … Read More

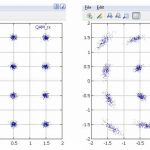

A tour of today’s Mixed-Signal solution

Mixed-Signal design is one of the very initial design methodologies, pioneered by Cadence with its lead in custom design; now taking centre space in the world of SoCs. Its growth is surmountable as it finds its place in most of the high growth electronics like smart phones, automotive applications, networks and communications,… Read More

Cadence IP Report Card 2013

The challenges of developing IP blocks, integrating them correctly, and hitting the power, performance, area, and time to market requirements of a mobile SoC is a growing problem. At 20nm and 14nm the probability of a chip re-spin due to an error is approaching 50% and we all know how disastrous a re-spin can be, those are not good … Read More

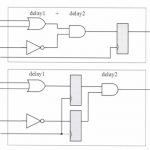

Plotting to take over the time-domain only world

The state machine nature of many digital designs has made time-domain debugging the favorite tool for most designers. We provide a set of inputs, data gets clocked in, and a set of outputs appears. We look for specific patterns in parallel paths, or sequences on serial lines.… Read More

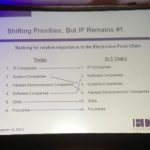

EDAC CEOs: consolidation, clouds, and whether Intel will buy Synopsys

Yesterday evening was the annual EDAC CEO forecast meeting. Actually it is not really a forecast meeting any more, more a sort of CEO response to some survey questions asked of EDAC members. Rich Valera of Needham moderated with Lip-Bu, Aart and Wally, along with Simon Segars representing the IP arm(!) of the business and Raul Camposano… Read More

Visual Debugging at Altera on Billion-Transistor Chips

My first job out of college was doing transistor-level circuit design, so I’m always curious about how companies are doing billion-transistor chip design and debug these days at the FPGA companies.

I spoke with Yaron Kretchmer,he works at Altera and manages the engineering infrastructure group where they have a compute… Read More

Costello on Communicating a Compelling Company Story

The next EDAC sponsored emerging company series (what I’ve been calling Hogan University) is Joe Costello being interviewed on how to communicate a compelling company story. Anyone who saw Joe’s keynote at DAC several years ago will not want to miss this. I can’t promise that he’ll lie down on the stage… Read More

IJTAG for IP Test: a free seminar

What: Better IP Test with IJTAG

When: 26 March, 2013, 10:30am-1:30pm

Where: Mentor Graphics, 46871 Bayside Parkway, Fremont, CA 94538

If you are involved in IC test*, you’ve probably heard about the IEEE P1687 standard, called IJTAG for ‘internal’ JTAG. IJTAG defines a standard for embedded IP that includes simple… Read More

ARM Cortex SoC Prototyping Platform for Industrial Applications

If your next SoC uses an ARM Cortex-A9 and has an industrial application, then you can save much design and debug time by using a prototyping platform. The price to prototype is quite affordable, and the methodology has a short learning curve. Bill Tomasan Aldec Research Engineer conducted a webinar today on: ARM Cortex SoC Prototyping… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior