Digital designers have used logic optimization and logic synthesis for decades as a means to produce more optimal designs with EDA tools. On the analog and transistor-level side of design the efforts to automatically optimize for speed or power have generally been limited to circuits with only a handful of transistors. These … Read More

Electronic Design Automation

Atrenta @ #51DAC Must See!

Last year at DAC, we launched the RTL Signoff platform and our customers responded enthusiastically. We even had a few other EDA companies follow our lead. So what have we been up to since then?

Visit us at DAC this June and learn how we have expanded our industry leading RTL Signoff solutions to handle the next set of challenges in SoC… Read More

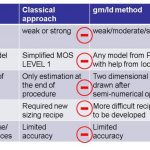

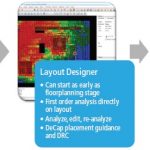

A Collaborative Approach Yields Better PI for PCBs

The power integrity (PI) of a system is an extremely important aspect to be looked at all levels – chip, package and PCB for overall reliability of the system. At the PCB level, a DC analysis, usually based on IR drop, must ensure that adequate DC voltage, satisfying all constraints of current density and temperature, is delivered… Read More

Low Power Design

So you want to do a low power design. Join the club. Who doesn’t? Today all designs are low power, it is the biggest constraint on what we can do on a chip. Power down; power domains, variable clock rates, mixed Vt libraries. Every trick is needed. And that is not even enough. We get to put our phones on charge each evening and there… Read More

Calypto @ #51DAC Must See!

DAC 2014 in San Francisco promises plenty of new information on emerging low power techniques and faster ways to get to working, fully verified RTL using high level synthesis and formal verification. Get the latest from the industry leader in technologies for high level design and verification and low power RTL designby attending… Read More

Panel: Strategies for Next Generation Semiconductor IP Management

I just returned from the “Semiconductor Executive Briefing: Strategies for Next Generation Semiconductor IP Management” panel,held at the Computer History Museum, sponsored by Dassault Systèmes.

(Left to right) Moderator: Warren Savage, President and CEO, IPextreme, with panelists John Tam, Director of Business Development,… Read More

Concept Engineering Showcases Effective SoC Debugging Techniques

In a complex environment of semiconductor design where an SoC can have several millions of gates and multiple number of IPs at different levels of abstractions from different sources integrated together, it becomes really difficult to understand and debug the overall SoC design. Of course, along with the SoC integration, optimization… Read More

Apache Design @ #51DAC Must See!

Register to hear industry experts from top semiconductor companies share their best practices that enable the next generation of high-performance, low power designs for mobile, automotive and other applications. Meet our technologists for in-depth presentations, case studies and demos on the industry’s leading simulation… Read More

Synopsys @ #51DAC Must See!

Accelerating Innovation—that has been at the heart of Synopsys’ commitment to its customers for more than 25 years. As a leader in EDA and semiconductor IP, Synopsys’ software, IP and services help engineers address their design, verification, system and manufacturing challenges and accelerate their innovations. Since 1986,… Read More

Cadence @ #51DAC Must See!

Cadence is excited to bring a full slate of demos, technical presentations, papers, and more to the Design Automation Conference (DAC) June 1-5, 2014, in San Francisco, CA. From our technical experts, you’ll learn tips and techniques from areas including low power, mixed signal, advanced nodes, signoff, verification, and IP,… Read More

Is Intel About to Take Flight?