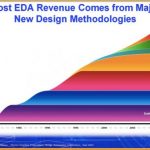

Wally Rhines gave the keynote at DAC in 2004. One of the things that he pointed out ten years ago was that EDA revenue for any given market segment is pretty much flat once the initial growth phase has taken place and the market has been established. Incremental EDA revenue only comes from delivering new capabilities. Historically… Read More

Electronic Design Automation

ESL Tool Update from #51DAC

As promised in my May 27th blog, I visited an ESL company at DAC three weeks ago that introduced two new tools:

- Thermal Profiler

- Power Intelligence

The Secret Essence of an IoT Design

Today the semiconductor industry along with electronics industry is looking up to capitalize from massive expansion foreseen in IoT (Internet of Things) domain. In simple terms we can consider IoT as connectivity between machines which can communicate with each other and work as programmed. In localized applications such … Read More

Intel Invests in the Fabless Ecosystem!

During my illustrious career one of the most useful axioms that I use just about everyday day is: “Understand what people say but also understand why they are saying it.” This certainly applies to press releases so let’s take a look at what Intel unleashed during #51DAC (in alphabetical order):

ANSYS And Intel Collaborate… Read More

ARC EM DSP supports Always-on Devices

The ARC EM family is the low-power, embedded and low footprint processor part of the larger ARC processor. To target the ultra low-power markets like wearable and IoT, Synopsys has added DSP capabilities to EM5D and EM7D. To be specific, these cores are optimized for ultra low-power control and DSP, thanks to:

- Energy-efficient

Enabling Technologies that Will Shape the next Wearables

One of the benefits of spending the last 30 years working in Silicon Valley and publishing a fabless semiconductor book is that I get invitations to speak at events I would normally be attending. Being on the other side of the podium is truly a unique experience and one worth pursuing, absolutely. This month I spoke at #51DAC about … Read More

Noise-Coupled Analysis for Automotive ICs at DAC

My favorite method to learn about EDA tools at DAC is by listening to actual IC designers, so on June 3rd I heard Jacob Bakker from NXP talk about his experience with noise coupled analysis for advanced mixed-signal automotive ICs.… Read More

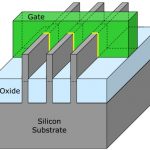

Intel & Ansys Enable 14nm Chip Production

In the semiconductor industry, it feels great to hear about the process technology shrinking to lower nodes along with innovative transistor structures that offer major gains in PPA (Power, Performance and Area). However, it requires huge investment of capital, time and effort from foundries to conceptualize, prototype and… Read More

Workshop: Embedded Applications and Kernels

Design Automation Conference Workshop on Suite of Embedded Applications and Kernels

In June, the first Suite of Embedded Applications and Kernels, or SEAK, workshop at the 2014 Design Automation Conference in San Francisco introduced a new Defense Advanced Research Projects Agency program in the area of embedded system benchmarking… Read More

SpyGlass CDC: A Comprehensive solution for addressing CDC issues

About a decade ago, semiconductor designs had just a few asynchronous clocks which were easily managed by designers through the process of manual design reviews. The situation today is completely different. An SoC can have hundreds of asynchronous clocks, driving different complex functions, spread across various IPs, supplied… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry