Our popular smart phones have a whole slew of RF-based radios in them for: Bluetooth, WiFi, LTE, GSM, NFC. Using just a single clock frequency for a DSP function or SoC is a thing of the past, so the design of multirate systems is here to stay. So now the challenge on the design and verification side is to use a methodology that supports:… Read More

Electronic Design Automation

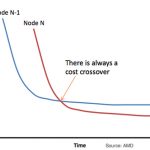

AMD Goes 3D

I attended the 3D packaging conference in Burlingame this week. The most interesting presentation to me was by Bryan Black of AMD. He argued very convincingly that Moore’s Law is basically over for the PC microprocessor business and the way forward is going to be 3D. AMD are clearly working on all this.

Increased density and… Read More

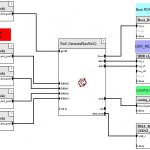

Taming The Interconnect In Real World For SoCs

Interconnect plays a significant role in the semiconductor design of a SoC; if not architected and handled well, it can lead to an overdesigned SoC impacting on its power, performance and area. Since a SoC generally contains multiple IPs requiring different data paths to satisfy varying latency and performance cycles, it has … Read More

Impact Conference: Focus on the IP Ecosystem

Jim Feldhan, President of Semico Research presented earlier this month at the Impact Conference on the topic: Focus on the IP Ecosystem. I’ve reviewed his 19 page presentation, and summarize it with:

- End markets like smart phones and tablets are dominant

- Growth drivers include the Internet of Things (IoT)

- World semi forecast

Known Unknowns and Unknown Unknowns

Donald Rumsfeld categorized what we knew into known unknowns and unknown unknowns. In a chip design, those unknown unknowns can bite you and leave you with a non-functional design, perhaps even intermittent failures which can be among the hardest problems to debug.

Chips are too big to do any sort of full gate-level simulation,… Read More

Designing a DDR3 System to Meet Timing

My very first thought when hearing about HSPICE is using it for IC simulation at the transistor-level, however it can also be used to simulate a package or PCB interconnect very accurately, like in the PCB layout of a DDR3 system where timing is critical. I attended a webinar this morning that was jointly presented by Zuken and Synopsys… Read More

Cadence CEO Keynotes DVCON 2014!

Next year’s DVCon attendees can expect to learn about both practical solutions to their pressing problems that can be applied today and also receive a preview of the technologies that will affect them in the near future. DVCON is March 3-6, 2014 @ the DoubleTree Hotel in San Jose.

KEYNOTE: An Executive View of Trends and Technologies… Read More

How to Assure Quality of Power and SI Verification?

As power has become one of the most important criteria in semiconductor design today, I was wondering whether there is a standard set for the power verification for an overall chip. We do have formats evolved like CPF and UPF and there are tools available to check power and signal integrity (SI), however I don’t see a standard objective… Read More

Capturing Analog Design Intent with Verification

Analog IC designers are gradually adopting what digital IC designers have been doing for years, metric driven verification. When you talk with analog designers about their methodology and approach, you hear terms like artisan being used which implies mostly a manually-oriented methodology. Thanks to automation from EDA companies,… Read More

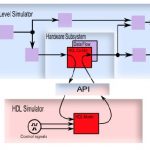

Virtual Prototypes Made Easier for SoC Design

Using a virtual prototype for your SoC design is accepted, conventional wisdom today because it can save development time by eliminating design iterations and avoid costly bugs that will cause an expensive product recall. In order to simulate your virtual prototype you need models, so a major question has always been, “Where… Read More

Flynn Was Right: How a 2003 Warning Foretold Today’s Architectural Pivot