Analog IC designers are gradually adopting what digital IC designers have been doing for years, metric driven verification. When you talk with analog designers about their methodology and approach, you hear terms like artisan being used which implies mostly a manually-oriented methodology. Thanks to automation from EDA companies, we are seeing more analog designers capturing their analog design intent with verification in mind. This week I spoke with Fouad Mkalech of Mentor Graphics to learn about an environment they offer called ICanalyst.

Fouad Mkalech, Mentor Graphics

Q: What is ICanalyst all about?

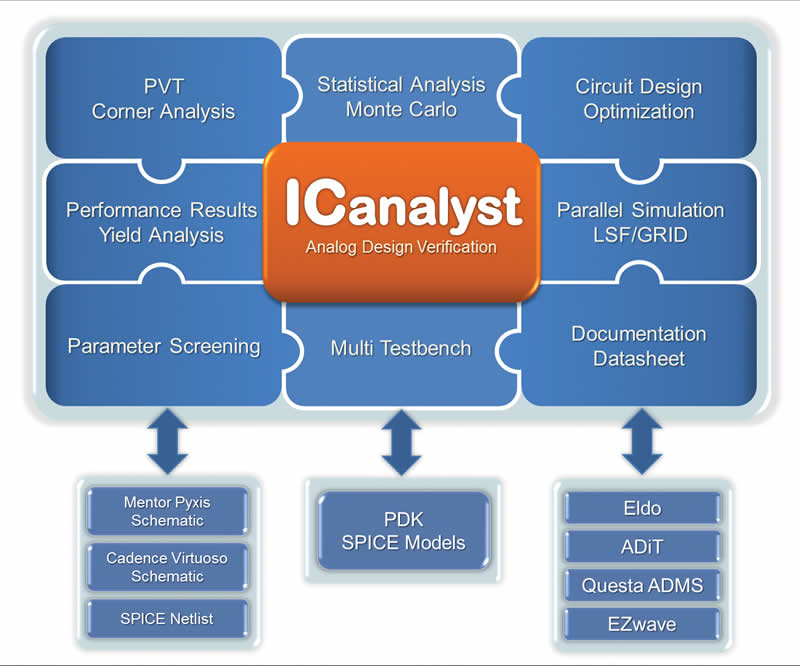

A: ICanalyst is something we’ve developed that is beyond just the traditional flow where you simulate a transistor netlist and then view waveforms. Metric driven verification is a very powerful concept used in digital design, so we’ve brought that idea over to analog IC designers. This tools provides a methodology for you to verify your analog design against the specifications.

Q: What changes would I make to my normal analog design flow?

A: You would start to use MEASURE and EXTRACT statements in your netlist, simulate, and then collect results into a database for analysis purposes, with both Digital and Analog domain results in one place.

Q: What kind of inputs are accepted in this process?

A: Design inputs include: Mentor Pyxis Schematic, Cadence Virtuoso schematic or just a SPICE netlist. Your SPICE circuit simulator also requires a PDK with the SPICE models.

Q: Which simulators are supported?

A: We support several simulators from Mentor: Eldo, ADiT, Questa ADMS.

Q: What are the benefits of analog design verification?

A: Designers now have the ability to input their requirements and then compare against simulated results in an automated fashion. It’s really quite similar to the UVM approach for digital designs in terms of creating a spec, adding requirements, then verifying in a testbench. This approach allows you to link the specification, test plan, and analog environment for measurements. You can then track your verification progress with ReqTracer using a requirement-driven process. Analog designers are no able to track down each requirement and see how it drives the test plan, and then answer the important question, “Is my design failing or passing this requirement?”

Q: Where is ICanalyst developed?

A: ICanalyst started out development in San Jose, and has now moved to Grenoble, France.

Q: Who would be the typical user of this tool?

A: Users include: analog designers, verification engineers or even project managers.

Q: What is the learning curve for ICanalyst?

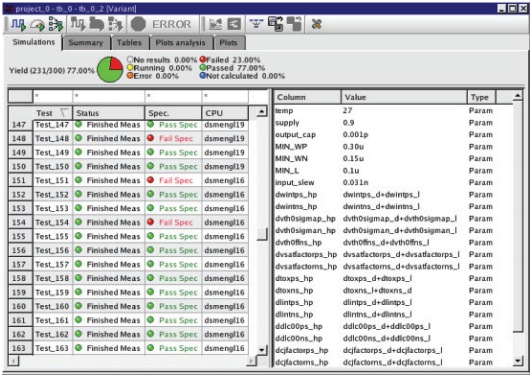

A: There’s a user interface, so it feels and looks intuitive. The general usage flow has: Create a spec, create Excel document with your requirements, import Excel, match measurements to tracking (SPICE measurements), results saved to a DB. We find that engineers are learning the tool within a day.

UI of ICanalyst: manage simulation setup, parallel job execution and results management

Q: What kind of questions can using ICanalyst help me answer?

A: One important question is, “Have I done enough analog circuit simulation to meet my specs?”

Q: Who has been using ICanalyst?

A: One customer is DENSO, they are a global supplier of automotive technology, systems and components.

Q: When is the next release of ICanalyst due?

A: In January we have our next release and it adds support of Requirements driven verification for analog design.

Q: Are there other EDA vendors with something similar to ICanalyst?

A: Yes, from Cadence there is a product called Virtuoso ADE XL.

More Articles by Daniel Payne …..

lang: en_US

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.