Some analysts are starting to get the idea that their credibility is worth something. Research firm IC Insights has actually dialed back its latest IoT semiconductor projection through 2019, although still calling for what would be quite robust overall growth.… Read More

Author: Don Dingee

NVIDIA looks inside Parker and automotive-grade

‘Parker’ is a fascinating name for a chip designed for autonomous vehicles – more likely, the project name was pulled off a map as a bedroom community near Denver. First highlighted on the roadmap in 2013, and advertised as inside the DRIVE PX 2 platform shown at CES 2016, NVIDIA revealed some details of Parker at Hot Chips 2016.… Read More

Pushing automotive-grade embedded flash to 28nm

18 months ago Renesas announced they were prototyping their SG-MONOS eFlash on 28nm, and at the time we said it would be a couple of years before actual product. Yesterday, Renesas revealed their partner in this effort is TSMC – no surprise – and hinted things are moving, with better performance than expected but on a longer qualification… Read More

AMD Zen and the Art of Microprocessor Maintenance

AMD is a fantastic company with highly talented people, but for some reason just hasn’t managed to put a winning streak of microprocessor architectures back-to-back. It’s frustrating to watch: they ride like mad to catch up to or even pull slightly ahead of Intel, then fall back in the pack when they have to make an extended pit stop,… Read More

Flex Logix validating EFLX on TSMC 40ULP

Flex Logix has been heads-down for the last several months working toward customer implementations of their EFLX reconfigurable RTL IP cores. Today, they’ve announced a family of 10 hard IP cores ready in TSMC 40ULP, and provided an update to their roadmap for us.… Read More

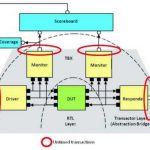

Striving for one code base in accelerated testbenches

Teams buy HDL simulation for best bang for the buck. Teams buy hardware emulation for the speed. We’ve talked previously about SCE-MI transactors as a standardized vehicle to connect the two approaches to get the benefits of both in an accelerated testbench – what else should be accounted for?… Read More

Customized PMICs with OTP in automotive and IoT

Power. Every device needs it. Managing it properly can make all the difference between a device people enjoy using and one that is more hassle than it is worth. What happens between the battery and the processor is the job of the power management integrated circuit (PMIC).

Why are PMICs gaining so much attention? Increased power … Read More

ARM gets wider and more flexible in vectors

ARM has a storied history of announcing major architecture changes at conferences far in advance of product implementations to get their ecosystem moving. At Hot Chips 2016, their sights are set on revamping the ARMv8-A architecture for a new generation of server and high-performance computing parallelism with a preview of … Read More

More on HAPS hybrid prototyping for ARMv8 with Linaro

A few weeks ago we previewed a Synopsys webinar describing how they are linking the ARM Juno Development Platform with the HAPS-80 and HAPS ProtoCompiler environment. I’ve had a look at the archived event and have some additional thoughts.… Read More

If an Intel 10nm transistor fell in the ARM forest

Intel’s news at IDF this week about partnering with ARM for foundry services on 10nm set off some wild speculation. It’s not a surprise that ARM would enable Intel – they’ve worked together before, ARM is an equal opportunity ecosystem partner, and ARM has publicly announced 10nm cores taped out at TSMC.… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era