In the semiconductor ecosystem, several partners (or better to say stakeholders) join together in the overall value chain to finally output the most coveted chip, err I should say SoC these days. It becomes really interesting when we start analyzing the real value added by each of them, none appears to be less. Well, then to whom … Read More

Tag: virtuoso

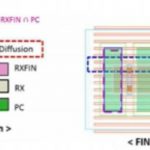

Samsung 14nm FinFET Design with Cadence Tools

The first consumer products with 20nm processing are arriving in 2014 like the 2 billion transistor A8 chip in the iPhone 6, however at the 14nm node there are new designs underway to continue the trend of Moore’s Law. To get a better feel for the challenges of designing with 14nm FinFET technology I watched a 23 minute video … Read More

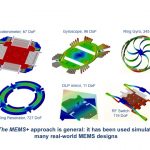

MEMS+, Bringing MEMS into the Electronic World

One of the things about MEMS devices is that they almost always live on a chip that also contains the electronics necessary to process the output from the sensor. For example, an on-chip accelerometer for a car airbag deployment will contain the electronics necessary to process the signal from the sensor and end up with something… Read More

Expert Tool to View and Debug Design Issues at Spice Level

Spice view of a design, block or fragment of the design is probably the lowest level of functional description of a circuit in terms of transistors, resistors, capacitors, interconnect and so on, which in several ways acts as an ultimate proof of pudding for any semiconductor design before manufacturing. However, it’s generally… Read More

FinFET Custom Design

At CDNLive, Bob Mullen of TSMC gave a presentation on their new custom FinFET flow, doing design, and verifying designs. At 16nm there are all sorts of relatively new verification problems such as layout dependent effects (LDE) and voltage dependent design rules. We had some of this at 20nm but like most things in semiconductor,… Read More

Automating Analog Verification in Virtuoso

Digital designers have been automating the functional verification process for many years now, however when you talk to an analog designer about how they do verification you quickly realize that the typical process is quite ad-hoc and little automated. Necessity does create an opportunity so the software engineers at Methodics… Read More

ARM, Cadence and the Internet of Things

There is clearly a lot of hype about the Internet of Things (IoT) right now, but also it is clear that it will be a real market. In fact, it already is with various medical, fitness and home-appliance products already available. At CES in January, wearables was probably the biggest trend. That doesn’t always pan out (3D TV was… Read More

High Quality PHY IPs Require Careful Management of Design Data and Processes

In last few years IP design has grown significantly compared to the rest of the semiconductor industry. There are newer IP start-ups opening across the world, particularly in India and China. Amid this rush, I wanted to understand the actual dynamics pushing this business and whether all of these IPs follow quality standards. … Read More

Parasitic Debugging in Complex Design – How Easy?

When we talk about parasitic, we talk about post layout design further expanded in terms of electrical components such as resistances and capacitances. In the semiconductor design environment where multiple parts of a design from different sources are assembled together into highly complex, high density SoC, imagine how complex… Read More

Data Management in Russia

Milandr is a company based in Moscow that makes high reliability semiconductor components for the aerospace, automotive and consumer markets, primarily in Russia. They work with multiple foundries, including X-FAB and TSMC in technologies from 1um down to 65nm. Corporate headquarter and main IC design house is located in Russian… Read More