On July 18, 2025, Serge Nicoleau from STMicroelectronics delivered a compelling presentation at DACtv, as seen in the YouTube video exploring how artificial intelligence (AI) is revolutionizing semiconductor design, edge computing, and sustainability. Addressing a diverse audience, Serge highlighted AI’s pervasive … Read More

Tag: st microelectronics

A Webinar with Silicon Catalyst, ST Microelectronics and an Exciting MEMS Development Contest

Most MEMS and sensor companies struggle to find an industrialization partner that can support early-stage research and help develop and transition unique concepts to high-volume production. The wrong partner means delays and increased development costs as the design moves between various facilities. Recently, Silicon … Read More

Next-Generation Formal Verification

As SoC and IP designs continue to increase in complexity while schedules accelerate, verification teams are looking for methodologies to improve design confidence more quickly. Formal verification techniques provide one route to improved design confidence, and the increase in papers and interest at industry conferences… Read More

Si Photonics in a 300mm Fab – This is Getting Serious!

Greater demand for more data exchange within data centers is being driven by mobile computing and the Internet-of-Everything. In 2011, it was estimated that over 1 Zettabytes (ZB) of data was pushed through the internet. That’s 1×10[SUP]21[/SUP] bytes of data. And, that amount has been doubling every 3 years since. Given… Read More

Thomas Skotnicki: FD-SOI 26 Years in the Making

It seems to be FD-SOI week yet again. I talked to Thomas Skotnicki this morning. He is the father of thin-box FD-SOI and its birth is an interesting story. The story began 26 years ago (so not quite as far back as the photo!).

Thomas is of Polish origins (he is actually Tomeczek) and grew up in Warsaw where he earned his PhD. In 1983 in Canterbury,… Read More

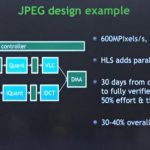

High Level Synthesis. Are We There Yet?

High level synthesis (HLS) seems to have been part of the backdrop of design automation for so long that it seems to be one of those things that nobody notices any more. But it has also crept up on people and gone from interesting technology to keep an eye on to getting genuine adoption. The first commercial product in the space was behavioral… Read More

FD-SOI the Synapse Way

Last week I talked to Marco Brambilla of Synapse Design. Synapse is a design services company headquartered in Silicon Valley. It was founded in 2003 by Satish Bagalkotkar and has been profitable since the beginning. Today it has over 700 people. In addition to the headquarters in Santa Clara, they have a software group in Colorado,… Read More

Grenoble Comes to San Francisco

The headquarters of ST Microelectronics is officially in Switzerland, but in many ways the center of gravity is in the Grenoble area. You may have heard of Crolles where ST does process development, manufacturing and more, which is about ten miles north-east of the city. As a result, along with the CEA-LETI and Grenoble Institute… Read More

FD-SOI Foundry

At the end of last month during ISSCC there was a forum organized by the SOI Consortium. It took place in San Francisco at the Palace Hotel (which, if you have never been there, is famous for converting its old entryway for carriages into an amazing dining room, and for a bar with a huge painting by Maxfield Parrish of the Pied Piper valued… Read More

FD-SOI at Samsung

Various foundries have made announcements about licensing FD-SOI technology from ST Microelectronics and then fallen quiet. GlobalFoundries made an announcement a couple of years ago. Samsung made an announcement just before DAC last year. But neither company has said anything much since. Of course the big noise at 14/16nm… Read More