This news in May 2014 that Samsung had licensed FD-SOI Technology from ST-Microelectronics was really amazing, as most of the industry was expecting this kind of agreement, but not with the #2 SC Company. But since May 2014 the news flow has been quite reduced, we can imagine that both SC companies had a lot work to do for transforming… Read More

Tag: st microelectronics

IEDM: FD-SOI Down to 10nm

The big picture is that planar semiconductor transistors don’t really work below 20nm. The reason is that the gate does a poor job of controlling the channel since too much channel is too far from the gate and so there is a lot of leakage even when the transistor is nominally off. So the channel needs to be made thinner. One way … Read More

FD-SOI, an Opportunity for China?

Last month in Shanghai was a meeting of the FD-SOI consortium. The focus of the meeting was largely on the suitability of using FD-SOI to serve the Chinese market. The fabs in China are not right on the bleeding edge and are very cost-sensitive so 28nm is probably as advanced as they will get for a long time if not indefinitely. China … Read More

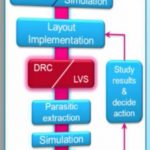

How ST Designs with Layout Dependent Effects (LDE)

I first visited STat their Agrate, Italy site where Flash memory development is done. At DACthis year Antonio Bogani talked about how ST designs with LDE while using EDA tools and a PDK (Process Design Kit) from Cadence. They recorded the 17 minute presentation, and you can view it herewithout having to register. Antonio’s… Read More

FD-SOI at 14nm

At the recent Semicon West, Michel Haond of ST Microelectronics had a presentation on 14nm FD-SOI, or what they more lengthily call UTBB FD-SOI (which when you expand it all out comes to Ultra Thin Body and Buried-Oxide Fully Depleted Silicon on Insulator). When Chenming Hu (or whoever in his group) came up with the term FinFET it … Read More

Analog Model Equivalence Checking Accelerates SoC Verification

In the race to reduce verification time for ever growing sizes of SoCs, various techniques are being adopted at different levels in the design chain, functional verification being of utmost priority. In an analog-digital mixed design, which is the case with most of the SoCs, the Spice simulation of analog components is the limiting… Read More

FD-SOI: 20nm Performance at 28nm Cost

There has been a lot of controversy about whether FD-SOI is or is not cheaper to manufacture than FinFET. Since right now FinFET is a 16nm process (22nm for Intel) and FD-SOI is, for now, a 28nm process it is not entirely clear how useful a comparison this is. Scotten Jones has very detailed process cost modeling software (that is what… Read More

FD-SOI Not Just For France Any More, China Signs On?

The COO of ST Microelectronics, Jean-Marc Chery announced that they have signed a new foundry agreement for FD-SOI. What he actually said doesn’t reveal who the foundry in question is:“We have just signed a strategic agreement with a top-tier foundry for 28nm FD-SOI technology. This agreement expands the ecosystem, assures… Read More

FD-SOI Better Than FinFET?

As I said earlier in the month, I was going to be talking about FD-SOI at the Electronic Design Process Symposium (EDPS) in Monterey. I am not especially an expert on FD-SOI but I know enough to be dangerous and given that we were already talking about FinFET and 3D/2.5D chips, it fitted in nicely.

The 10,000 foot view is that FD-SOI has… Read More

ISSCC: Analog-Digital Converter in FD-SOI

The International Solid-State Circuits Conference (ISSCC) was last week in San Francisco. Stéphane Le Tual, Pratap Narayan Singh, Christophe Curis, Pierre Dautriche, all from STMicroelectronics presented a paper on A 20GHz-BW 6b 10GS/s 32mW Time-Interleaved SAR ADC with Master T&H in 28nm UTBB FDSOI Technology… Read More