In the semiconductor industry High-Level Synthesis (HLS) and SystemC have become essential tools, allowing engineers to model complex hardware designs using familiar C/C++ constructs. Yet, despite the widespread adoption of these languages, the debugging workflows in hardware development lag far behind those in software… Read More

Tag: high-level synthesis

SystemC Update 2024

SystemC version 1.0 came out in 2000 as a C++ class library for system-level modeling and simulation, and on SemiWiki.com there are some 497 references to the language. I wanted to provide an update in this blog so that engineering teams can become more efficient in using SystemC on their SoC projects, saving time and improving product… Read More

Emerging Stronger from the Downturn

It was refreshing to hear a talk focused on emerging stronger from the downturn when the news and media are focused on the gloom. At the recent Siemens EDA User2User conference, Joe Sawicki, executive vice president, IC, gave an uplifting keynote talk to the audience. He highlighted a secular growth trend happening in the semiconductor… Read More

Synopsys Presents SAT-Sweeping Enhancements for Logic Synthesis

There was a “research reviewed” panel on Thursday at DAC entitled Shortening the Wires Between High-Level Synthesis and Logic Synthesis. Chaired by Alric Althoff of Tortuga Logic, the panel explored methods to deal with wire delays in high-level synthesis and logic synthesis. The four speakers and their focus were:

- Licheng

Mentor Highlights HLS Customer Use in Automotive Applications

I’ve talked before about Mentor’s work in high-level synthesis (HLS) and machine learning (ML). An important advantage of HLS in these applications is its ability to very quickly adapt and optimize architecture and verify an implementation to an objective in a highly dynamic domain. Design for automotive applications – for … Read More

Specialized AI Processor IP Design with HLS

Intelligence as in the term artificial intelligence (AI) involves learning or training, depending on which perspective it is viewed from –and it has many nuances. As the basis of most deep learning methods, neural network based learning algorithms have gained usage traction, when it was shown that training with deep neural network… Read More

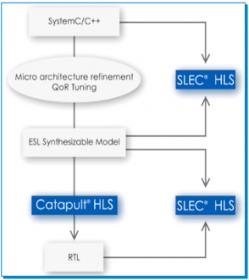

Sequential Equivalency Checks in HLS

Higher level synthesis (HLS) of an IP block involves taking its high-level design specification –usually captured in SystemC or C++, synthesizes and generates its RTL equivalent. HLS provides a faster convergence path to design code stability, promotes design reuse and lowers front-end design inception cost.

HLS and Mentor… Read More

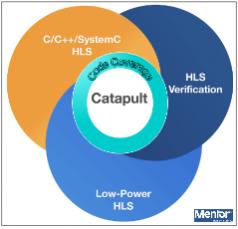

Closing Coverage in HLS

Coverage is a common metric with many manifestation. During the ‘90s, both fault and test coverage were mainstream DFT (Design For Testability) terminologies used to indicate the percentage of a design being observable or tested. Its pervasive use was then spilled over into other design segments such as code coverage, formal… Read More

High-Level Synthesis for Automotive SoCs

Some of the world’s most complex Systems-on-Chip (SoCs) are being developed for automotive applications. These SoCs have heterogeneous architectures with a variety of processors and accelerators that do real-time image processing for assisted and autonomous driving applications. The Bosch Visiontec team, in Sophia Antipolis,… Read More

Xilinx is a Software Company

If you think of Xilinx the word that immediately comes to mind is FPGA. After all they were one of the pioneers of the space. FPGAs are a means of implementing hardware, and the main implementation methodology is RTL-based. This compares to writing software and compiling it for a microprocessor, which is the main software implementation… Read More