High level synthesis (HLS) seems to have been part of the backdrop of design automation for so long that it seems to be one of those things that nobody notices any more. But it has also crept up on people and gone from interesting technology to keep an eye on to getting genuine adoption. The first commercial product in the space was behavioral… Read More

Tag: high-level synthesis

NVIDIA and Qualcomm Talk about High Level Synthesis, Samsung on Low Power for Mobile

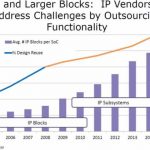

Since 1978 I’ve seen many trends in the semiconductor design world: transistor-level IC design, gate-level design, RTL coding, High Level Synthesis (HLS) and IP re-use. We’ve witnessed the growth in design productivity enabling chips starting with just thousands of transistor all the way up to billions of transistors… Read More

Shorten the Learning Curve for High Level Synthesis

When chip designers moved from a gate-level design methodology to coding with RTL there was a learning curve involved, and the same thing happens when you move from RTL to High Level Synthesis (HLS) using C++ or SystemC coding. One great shortcut to this learning curve is the use of pre-defined library functions. I just heard about… Read More

High Level Synthesis update from #51DAC

Every since Synopsys dominated the logic synthesis market in the 1980’s we’ve had something called HLS – High Level Synthesis, meaning something higher than what Design Compiler can understand as input. At DACthis year I met with Mark Milligan of Calypto to get an update on what’s new with HLS. I first… Read More

Calypto: the View From the Top

At DVCon today I talked to Sanjiv Kaul, the CEO of Calypto. Just as a reminder, Calypto have 3 products, SLEC (sequential logical equivalence checking, also called sequential formal verification), PowerPro (sequential RTL level power reduction) and Catapult High Level Synthesis (that they took over from Mentor in 2011 in a complicated… Read More

6 reasons Synopsys covets C/C++ static analysis

By now, you’ve probably seen the news on Synopsys acquiring Coverity, and a few thoughts from our own Paul McLellan and Daniel Payne in commentary, who I respect deeply – and I’m guessing there are many like them out there in the EDA community scratching their heads a little or a lot at this. I’m not from corporate, but I am here… Read More

Cadence Acquires Forte

Cadence today announced that it is acquiring Forte Design Systems. Forte was the earliest of the high-level synthesis (HLS) companies. There were earlier products. Synopsys had Behavioral Compiler and Cadence had a product whose name I forget (Visual Architect?), but both products were too early and were canceled. Cadence … Read More

Addressing Power at Architectural and RTL Levels

Major power reductions are possible by reducing power at the RTL and system levels, and not just at the gate and physical level. In fact, as is so often the case in design, changes can have much more impact when done at the higher level, even given that at that point in the design there is less accurate feedback about changes. Later the… Read More

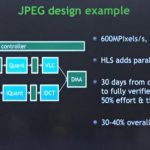

Using HLS to Turbocharge Verification

One of the benefits of using high-level synthesis is obviously the ease of writing some algorithms in SystemC since it is at a higher level than RTL (that’s why we call it high-level synthesis!). But a second benefit is at the verification level. Since a lot of the verification gets done at the SystemC level, less needs to be done at … Read More

What Applications Implement Best with High Level Synthesis?

RTL coding using languages like Verilog and VHDL have been around since the 1980’s and for almost as long a time we’ve been hearing about High Level Synthesis, or HLS that allows an SoC designer to code above the RTL level where you code at the algorithm level. The most popular HLS languages today are C, C++ and SystemC.… Read More