Ann Kelleher is Intel’s Executive Vice President, General Manager, Technology Development, and she gave the first plenary talk to kick off the 2022 IEDM, “Celebrating 75 Years of the Transistor A Look at the Evolution of Moore’s Law Innovation”. I am generally not a fan of plenary talks because I think they are often too broad and general without any real information, but I thought this was a good talk.

She started with the messages that Moore’s law is critical to addressing the needs of computing, that System Technology Co-Optimization (STCO) is the next major evolution of Moore’s law and that there are many challenges to overcome.

She went on to review some of the innovations in device structures and all the products they have enabled.

In her view Moore’s law has gone through four evolutions:

- Evolution 1 – geometric scaling. This was the classic Denard scaling era when a geometric shrink of a transistor improved power, performance, and area.

- Evolution 2 – as scaling of certain elements of a transistor began to reach limits, novel materials and device structures were introduced to continue scaling. This was innovations like strain and HKMG, and the transition to FinFETs.

- Evolution 3 – Design Technology Co-Optimization – co-optimization of the device design and process. For example, shrinking cell height requires fin depopulation and that reduces performance unless the process is improved to compensate. The last several years have seen DTCO becoming increasingly important.

- Evolution 4 – System Technology Co-Optimization – just optimizing the device is no longer enough and we need to optimize the entire system!

She gave an example of STCO where chiplets, IP design and validation are DTCO with process technology, and are combined with package, chiplet design and validation integrated with packaging technology, along with software and hardware architecture and validation, to produce an optimized system.

- A device includes process technology, transistor & interconnect and foundational IP.

- DTCO adds core & accelerator IP and chiplets.

- STCO further adds advanced packaging, system architecture, software and applications and workload.

There are many opportunities for innovation:

- People – highlighted as the most important, people are the drivers of innovation.

- Scaling – Ribbon FETS and then CFETs.

- Interconnect – RC delay, electromigration, photonics.

- Materials – metals, dipoles, photoresist, dielectrics.

- Patterning EUV then High-NA, then multi-patterning with EUV and eventually High-NA.

- Memory – power loss during transfer, compute in memory, optical, ferroelectric.

- Disaggregation – chiplets/tiles, reliability.

- Packaging/Assembly, Test – 2.5D packaging, 3D packaging, EMiB + Foveros = Ponte Vecchio (47 tiles from 5 process nodes), optical.

- Reliability – any changes must be evaluated for reliability, 3D packaging – power and thermal.

- Software – very important for delivering product, need to take software into account when doing STCO.

- Manufacturing – when looking at material take sustainability into account.

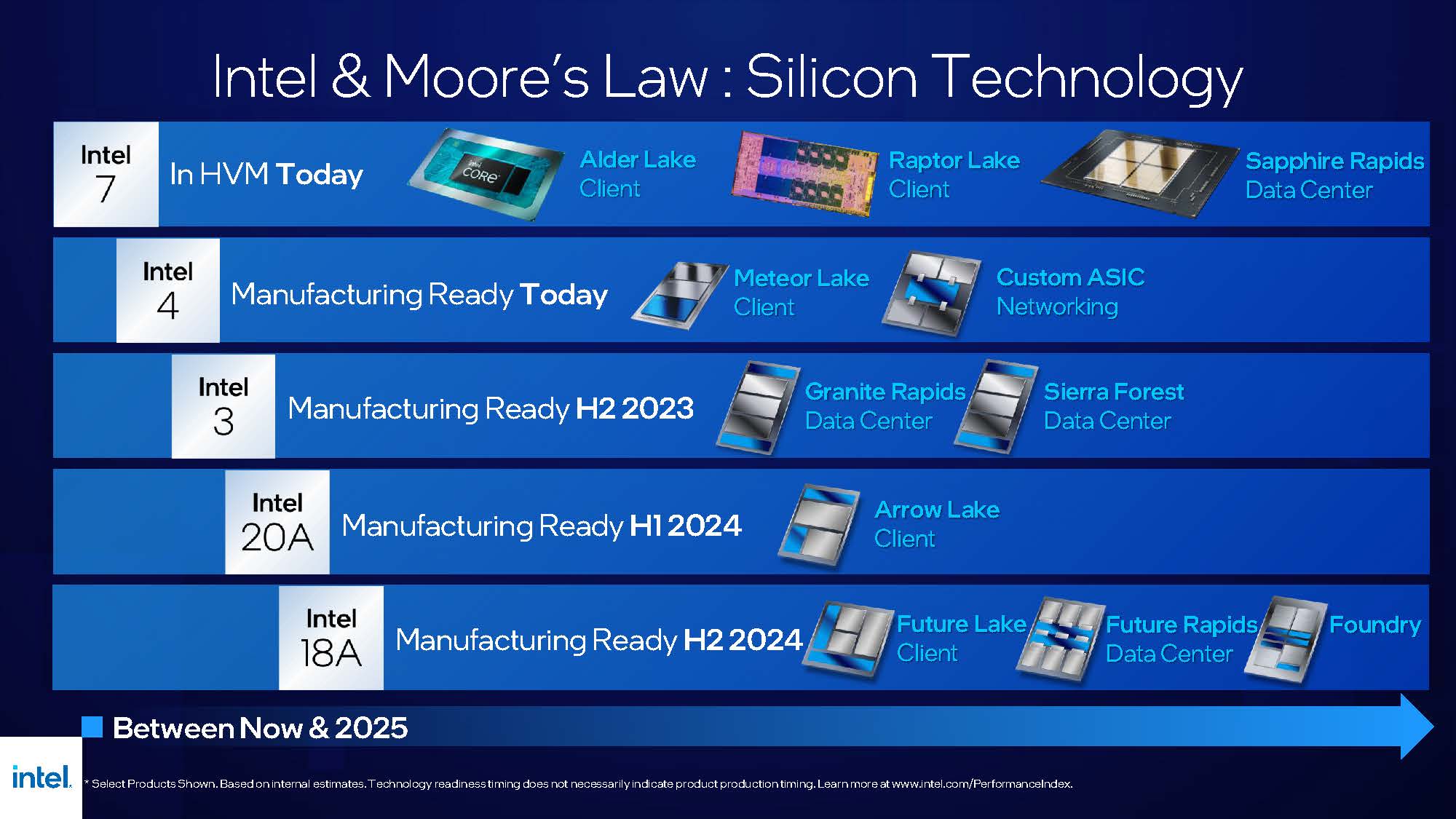

Figure 1 illustrates how Intel is delivering on silicon technology and the resulting products.

Figure 1. Intel & Moore’s Law: Silicon Technology.

Figure 1 illustrates that Intel continues to be on track to meet their silicon roadmap. I was skeptical Intel could meet the original Intel accelerated timeline, then they pulled it in (18A moved from 2025 to the second half of 2024), and so far, they are meeting it. I am very impressed that Ann and her team are executing at such a high level after a decade of delays at Intel.

On the packaging front Intel is working on Foveros Direct for the second half of 2023, with a 10x higher bump density versus the current Foveros process, alongside higher bandwidth, lower latency, lower power and smaller die area. Intel is also working on pluggable optical interconnect.

Longer term Intel research is working on:

- Enabling seamless integration of chiplets with an additional 10x improvement in density and placement flexibility.

- Super thin materials to further scale beyond RibbonFET by implementing 2D materials (this is a hot topic at the conference with multiple papers from Intel, TSMC and others).

- New possibilities in energy efficiency with more energy efficient memory such as FeRAM (another hot topic), magento electric devices and GaN on silicon.

In summary Ann Kelleher presented a fascinating view of the opportunities and challenges to continue Moore’s law for another decade or more. Intel is clearly back as a leading technology innovator.

Also Read:

Intel Foundry Services Forms Alliance to Enable National Security, Government Applications

Intel and TSMC do not Slow 3nm Expansion

3D Device Technology Development

Share this post via:

Comments

7 Replies to “IEDM 2022 – Ann Kelleher of Intel – Plenary Talk”

You must register or log in to view/post comments.