We’ve been talking about the different technologies for FPGA-based SoC prototyping a lot here in SemiWiki. On the surface, the recent stories all start off pretty much the same: big box, Xilinx Virtex-7, wanna go fast and see more of what’s going on in the design. This is not another one of those stories. I recently sat down with Mick… Read More

All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read More

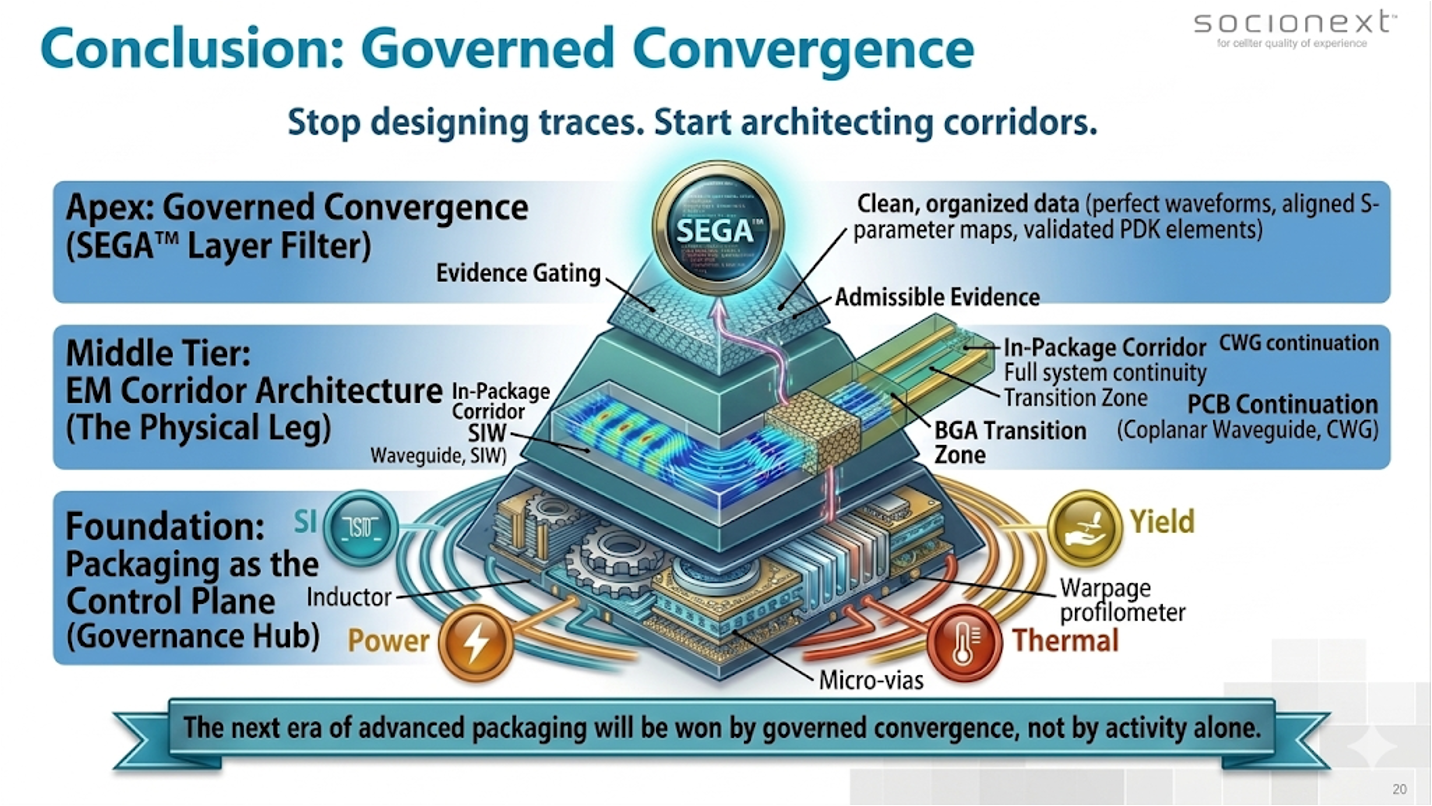

All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read More Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet GovernanceBy Dr. Moh Kolbehdari Dr. Moh Kolbehdari is…Read More

Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet GovernanceBy Dr. Moh Kolbehdari Dr. Moh Kolbehdari is…Read More SemiWiki Q&A with Julie Rogers, Executive Director, ESD AllianceThe Electronic System Design Alliance (ESD Alliance), a SEMI…Read More

SemiWiki Q&A with Julie Rogers, Executive Director, ESD AllianceThe Electronic System Design Alliance (ESD Alliance), a SEMI…Read MoreA Brief History of ClioSoft

In the 1990s, software developers were established users of software configuration management (SCM) tools such as open source RCS/CVS or of commercial systems such as Clearcase. Hardware designers, however, managed design data in ad hoc home-grown ways. ClioSoft’s founder, Srinath Anantharaman, recognized that hardware… Read More

SemiWiki Hits Major Readership Milestone!

For those of you who follow SemiWiki and the fabless semiconductor ecosystem it has been a very interesting two years:

The Semiconductor Wiki Project, the premier semiconductor collaboration site, is a growing online community of professionals involved with the semiconductor design and manufacturing ecosystem. Since going… Read More

Common Platform Technology Forum February 5th 2013 Live or Online!

Can’t make it to Santa Clara? Join us online!

The detailed 2013 CPTF agenda is now up in preparation for the February 5th event at the Santa Clara Convention Center. This is one of the rare times that you can get a free lunch! Watch this quick video to see what is in store for us this year. Dr. Paul McLellan and I will be there so please… Read More

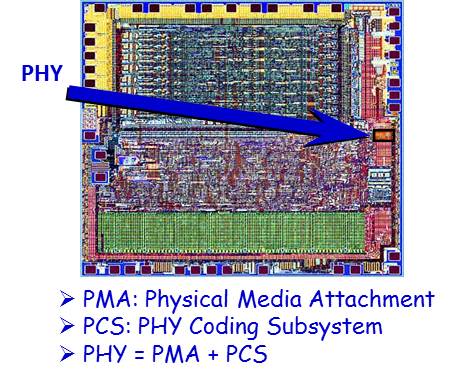

Design IP including Multi-standard SerDes enables risk-free, faster customer ASIC designs

ASIC design service companies are an essential piece of the SC ecosystem, as well as Silicon Foundries, EDA and IP vendors. Their customers range from pure fabless with no ASIC design resources, who need a third party to turn a concept into a real product (IC) and then market and sale it, to large IDM temporarily lacking design resource… Read More

Startups: the Biggest Challenge

What is the biggest challenge facing an EDA startup today? By a startup, I mean a brand new company, not a company that already has a few customers and is either on a fast path to success or a slower path whereby the company can continue to grow slowly forever.

Obviously, one challenge is the funding environment. Since EDA acquisitions… Read More

Seeing inside SoC designs, from the beginning

Engineers have this fascination with how things work. They are thrilled to tear stuff apart, and sometimes to even be able to put it back together afterwords. So I can keep my recovering engineer card, I thought I’d take a few moments and look inside a technology Daniel Payne and I have been covering here, exploring where the idea started… Read More

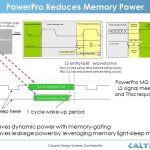

Dynamic/Leakage Power Reduction in Memories

Embedded memories have an important impact on power. SoCs that integrate multiple functions on a single silicon die are at the heart of many electronic devices. As process geometries have scaled, design teams have used more and more of the additional silicon real estate available to integrate embedded memories that serve as scratch-pads,… Read More

TSMC ♥ Oasys

Oasys has joined the TSMC Soft-IP Alliance Program. This means that TSMC IP partners have access to a new RTL exploration tool to improve QoR and reduce the iterations needed for design closure. In modern process nodes, RTL engineers implementing complex IP cores for graphics, networking, and mobile computing are struggling … Read More

Advanced Technology-Design-Manufacturing Co-optimization

I spent some quality time with Subi Kengeri, Vice President, Technology Architecture, Office of the CTO, GLOBALFOUNDRIES in Las Vegas during CES. Great guy, he worked at Silicon Access, Virage and TSMC before GF. One thing you should know about embedded memory guys, SRAM is the first thing that goes through a new process so they … Read More

Solving the EDA tool fragmentation crisis