Jump into Xilinx Programmable Logic today! I wanted to encourage my dear readers if you have not tried using an Xilinx FPGA (Field Programmable Gate Array) or even CPLD (Complex Programmable Logic Device) then it is worth your time to begin your evaluation. Maybe you got one for Christmas? If not, it is easier than you think to start… Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read MorePatterns looking inside, not just between, logic cells

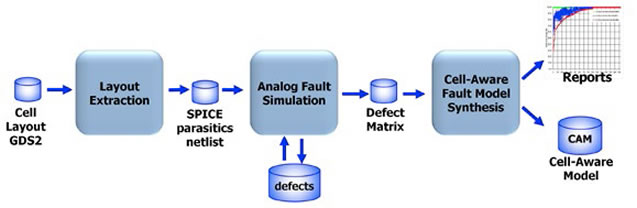

Traditional logic testing relies on blasting pattern after pattern at the inputs, trying to exercise combinations to shake faults out of logic and hopefully have them manifested at an observable pin, be it a test point or a final output stage. It’s a remarkably inefficient process with a lot of randomness and luck involved.

Getting… Read More

Smart Watch, Phone, Phablet, Tablet, Thin Notebook…?

There are more, but wait a while, from this set which ones do you need? Or let me ask the question differently (I know you may like something impulsively and have money to buy), which ones do you want to buy and own? Still confused? I guess what you need, you already have, but you want to change it for something new and different. While I … Read More

Highest Test Quality in Shortest Time – It’s Possible!

Traditionally ATPG (Automatic Test Pattern Generation) and BIST (Built-In-Self-Test) are the two approaches for testing the whole semiconductor design squeezed on an IC; ATPG requires external test equipment and test vectors to test targeted faults, BIST circuit is implemented on chip along with the functional logic of IC.… Read More

A little FPGA-based prototyping takes the eXpress

Ever sat around waiting for a time slot on the one piece of big, powerful, expensive engineering equipment everyone in the building wants to use? It’s frustrating for engineers, and a project manager’s nightmare: a tool that can deliver big results, and a lot of schedule juggling.… Read More

Social Media at Silvaco

Founded back in 1984, Silvaco has been in business for some 29 years now, focusing on the TCAD and EDA markets.

Browsing their Home page at www.silvaco.com we find four social media links in the footer: Facebook, Twitter, YouTube and LinkedIn.… Read More

SLEC is Not LEC

One of the questions that Calypto is asked all the time is what is the difference between sequential logical equivalence checking (SLEC) and logical equivalence checking (LEC).

LEC is the type of equivalence checking that has been around for 20 years, although like all EDA technologies gradually getting more powerful. LEC is … Read More

Semicon Technology Advancement – A View From IEDM

As I see the semiconductor industry going through significant changes and advances, yet ironically plagued by a growing perception that the pace of scaling is slowing, I was inclined to take a peek into what the industry experts say about the state of the industry and the future of Moore’s Law. Fortunately, at last week’s International… Read More

EDA and Semi IP Stocks in 2013: MENT, ARMH, CDN, SNPS, ANSS, CEVA, IMG.L

2013 was an up year for the stock markets as both the DJIA and the tech-heavy NASDAQ showed significant growth, so how did EDA and Semi IP companies do in the past 12 months? A quick stock plot from Yahoo Finance shows us that only two of the seven companies beat the NASDAQ: ARMH, MENT.… Read More

Semiconductor equipment back on track

Global semiconductor manufacturing equipment sales have increased each of the last three quarters after dropping significantly in the second half of 2012, based on data from Semiconductor Equipment and Materials International (SEMI) and Semiconductor Equipment Association of Japan (SEAJ). Much of the volatility is in sales… Read More

Solving the EDA tool fragmentation crisis