A common SoC design methodology in current use starts with preparation of the physical floorplan — e.g., block/pin placement, global clock domain and bus signal planning, developing the global/local power distribution (and dynamic power domain management techniques). Decoupling capacitor estimated densities and… Read More

UX in Agentic Systems. Innovation in VerificationA switch this month to principles behind building…Read More

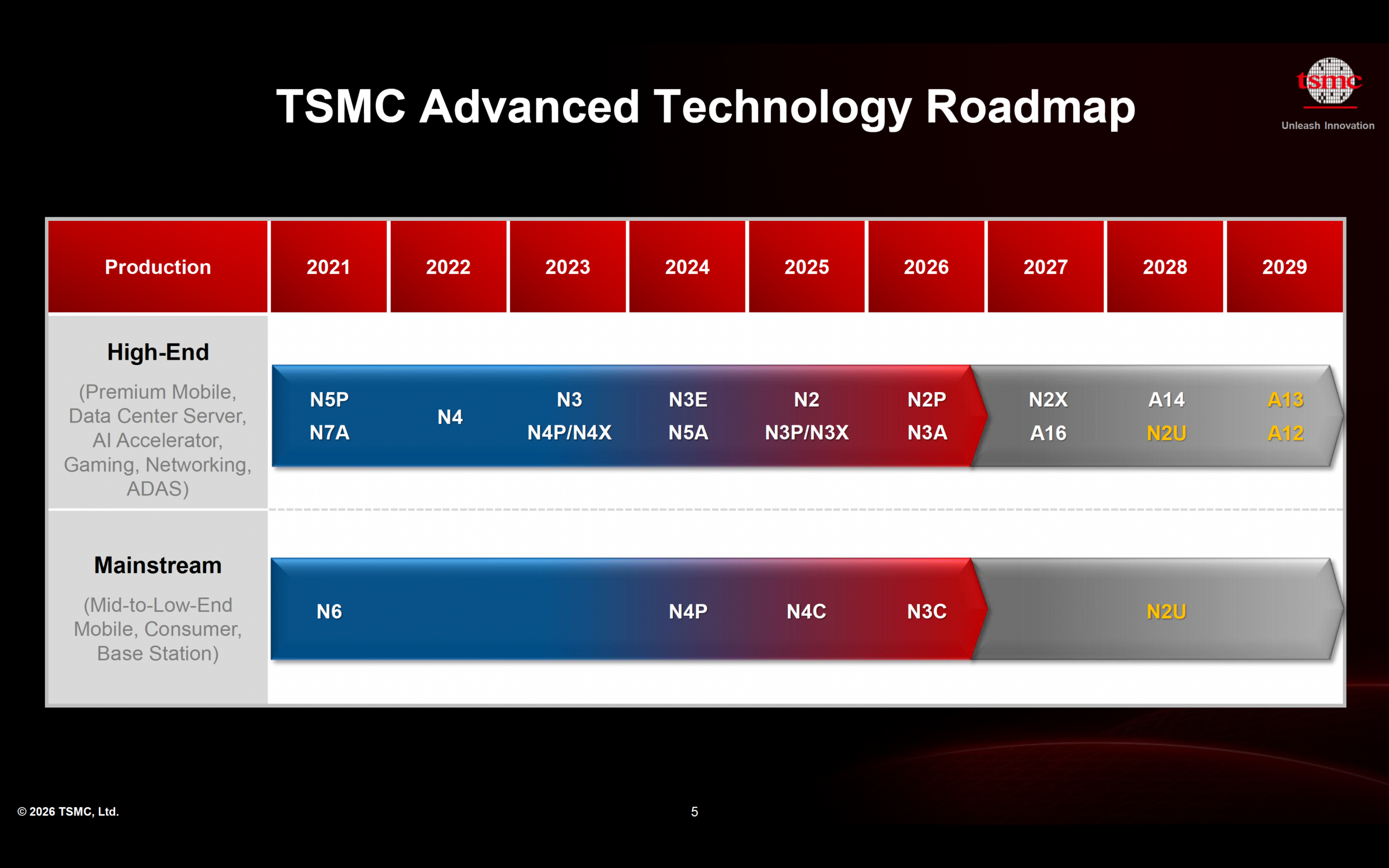

UX in Agentic Systems. Innovation in VerificationA switch this month to principles behind building…Read More The Shift to System-Level AI Drives Next-Generation SiliconAt its 2026 Technology Symposium, TSMC delivered a…Read More

The Shift to System-Level AI Drives Next-Generation SiliconAt its 2026 Technology Symposium, TSMC delivered a…Read More All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read More

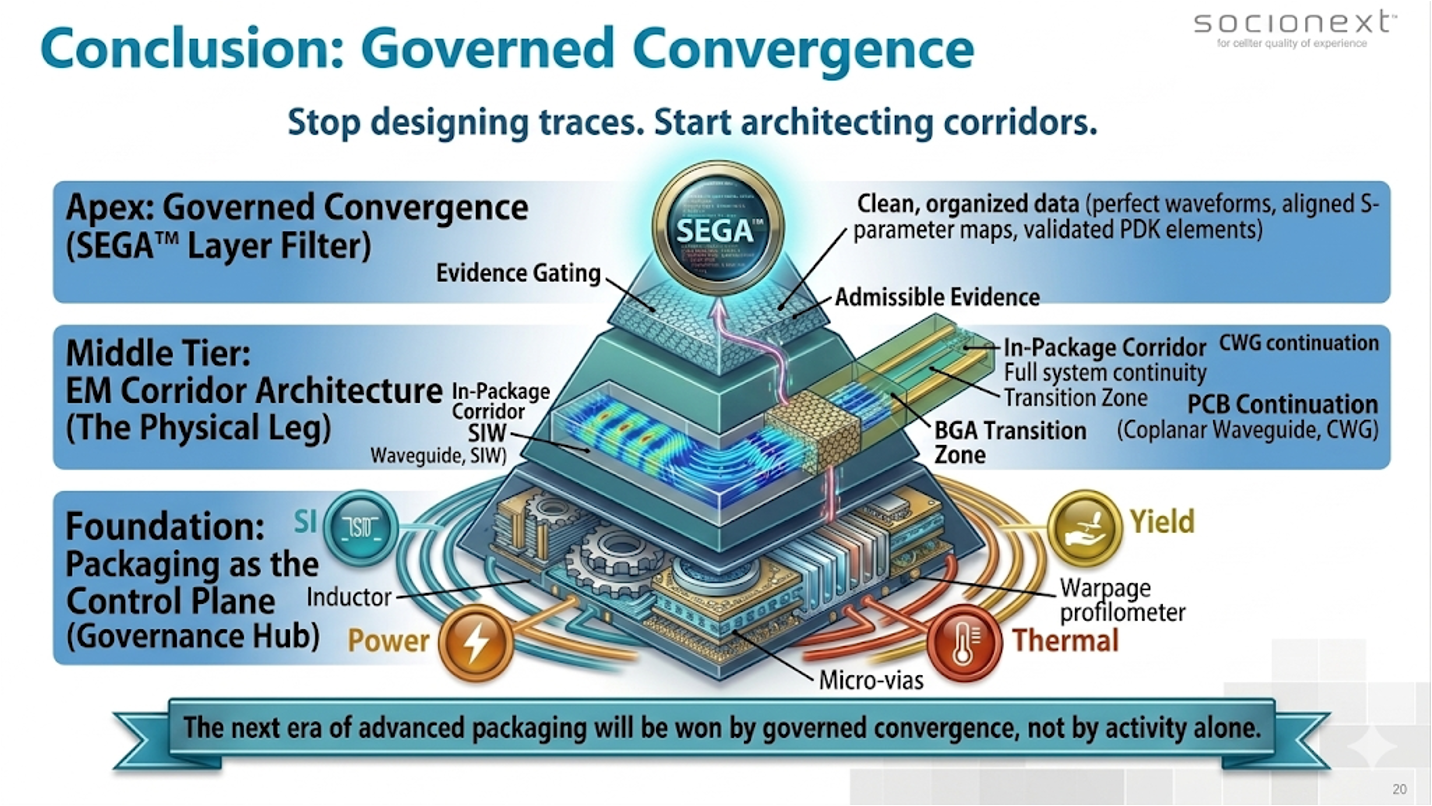

All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read More Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet GovernanceBy Dr. Moh Kolbehdari Dr. Moh Kolbehdari is…Read More

Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet GovernanceBy Dr. Moh Kolbehdari Dr. Moh Kolbehdari is…Read More SemiWiki Q&A with Julie Rogers, Executive Director, ESD AllianceThe Electronic System Design Alliance (ESD Alliance), a SEMI…Read More

SemiWiki Q&A with Julie Rogers, Executive Director, ESD AllianceThe Electronic System Design Alliance (ESD Alliance), a SEMI…Read MoreRebooting EDA

In the 35 years since commercial EDA went mainstream a lot of advances have been made but the fundamental architecture and even the philosophy of tooling have really not advanced at all. Tools are designed around individual tasks – analysis and optimization within a specific domain – under the assumption that variability within… Read More

Google TPU Another Step in a Shifting Semiconductor Landscape

Markets work when consumers of a widget don’t feel there is significant differentiated value in making their own and would rather get lowest possible cost from experienced widget makers who can amortize their investment over high-volume sales to many customers. But that changes when a large consumer finds they can increase differentiated… Read More

Ride Hailing is Not Ride Sharing

There are many misconceptions about ride sharing as journalists and analysts are wont to refer to Uber, Lyft, DiDi and the rest. Conceived as a means to increase asset utilization by allowing drivers to pick up passengers along their way, ride sharing services instantly became ride hailing services directly competing with taxis… Read More

Where are the Entrepreneurs?

This week I attended the UpWest Labs event in San Francisco. UpWest Labs provides seed funding and incubation for a wide range of domains including Enterprise Software, Internet of Things, Infrastructure Technologies, Artificial Intelligence, Consumer Applications, Drones, Cyber Security, Augmented Reality / Virtual … Read More

Donald Trump’s demand that Apple must make iPhones in the U.S. actually isn’t that crazy

Donald Trump has promised that “we’re gonna get Apple to start building their damn computers and things in this country, instead of in other countries.” He said this ata speech at Virginia’s Liberty University andseveralother events. It is very likely that he is not serious; Trump tends to say things he couldn’t possibly mean. … Read More

Aldec extends FPGA and ASIC flows at DAC

Aldec tools and services have long been associated with FPGA designs. As FPGAs have evolved toward more RTL-based designs, the similarities between a modern FPGA verification flow and an ASIC verification flow often leave them looking virtually the same. … Read More

Cache Coherent Systems Get a Boost from New Technology

The speed and power penalties for accessing system RAM affect everything from artificial intelligence platforms to IoT sensor nodes. There is a huge power and performance overhead when the various IP blocks in an SOC need to go to DRAM. Memory caches have become essential to SOC design to reduce these adverse effects. However, … Read More

Stop FinFET Design Variation @ #53DAC and get a free book!

If you plan on visiting Solido (the world leader in EDA software for variation-aware design of integrated circuits) at the Design Automation Conference next month for a demonstration of Variation Designer, register online now and get an autographed copy of “Mobile Unleashed”. Such a deal!

Solido Variation Designer is used by… Read More

Internet of Things Tutorial: Chapter Three

Emerging and future Internet-of-Things (IoT) systems will increasingly comprise mulitple heterogeneous internet connected objects (e.g., sensors), which will be operating across multiple layers (e.g., consider a camera providing a view of a large urban area and another focusing on a more specific location within the same… Read More

Solving the EDA tool fragmentation crisis