You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

This is the thirteenth in the series of “20 Questions with Wally Rhines”

My development of a calculator program to determine the Black Scholes value for an option was not the only application that attracted financial people to programmable calculators. As the SR-52, and later TI 59, grew in popularity, and took market… Read More

Transistor-level design for full-custom and analog circuits has long been a way for IC design companies to get the absolute best performance out of silicon and keep ahead of the competition. One challenge to circuit designers is meeting all of the specs across all Process, Voltage and Temperature (PVT) corners, so that silicon… Read More

Moshe Sheier, VP Marketing at CEVA, recently got back from MWC Shanghai and commented that robots are clearly trending. He saw hordes of robots from dozens of companies, begging for someone to brand and offer them in any one of many possible applications: in an airport to guide you to a connecting flight, for elder care, in hospitals… Read More

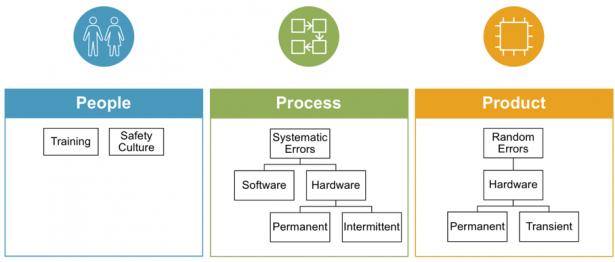

Kurt Shuler, VP Marketing at Arteris IP, is pretty passionate that people working in the automotive supply chain should understand not just a minimalist reading of ISO 26262 as it applies to them but rather the broader intent, particularly as it is likely to affect others higher in the supply chain. As an active ISO 26262 working … Read More

There are tectonic changes happening in the world of FPGAs. A lot has changed since their introduction in the 80’s. Back then they were mostly used to implement state machines or glue logic. Subsequently they grew more complex with the addition of high speed IOs, eRAM, DSPs, other processors and other IP. More recently though FPGAs… Read More

Designers require comprehensive logical, physical, and electrical models to interpret the results of full-chip power noise and electromigration analysis flows, and subsequently deduce the appropriate design updates to address any analysis issues. These models include: LEF, DEF, Liberty library models (including detailed… Read More

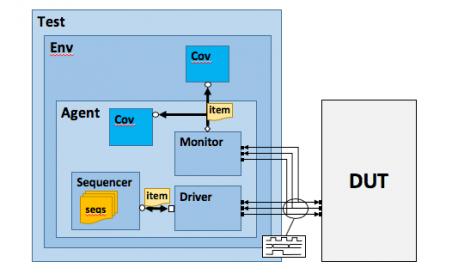

Something I always admire about Mentor is their willingness to invest their time and money in helping the industry at large. They do this especially in verification where they sponsor periodic Wilson surveys on the state of verification needs and usage in the industry. More recently they introduced their UVM Cookbook, an introduction… Read More

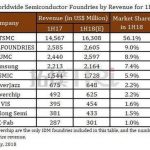

It’s no secret that I have been a big fan of GLOBALFOUNDRIES since they came about in March of 2009. We even included them in our first book “Fabless: The Transformation of the Semiconductor Industry” right next to TSMC. I am also a big fan of pivoting which is the term we use here in Silicon Valley to describe some of the most innovative… Read More

Could this be more bad news for semicap spend? Negative for US chip independence & AMD costs ? Rumors of Global Foundries dropping out of the 7NM race have been increasing rapidly. What could be a fatal blow to the GloFo 7NM program was AMD deciding to go with TSMC for 7NM first for one product and finally for its next generation CPUs.… Read More

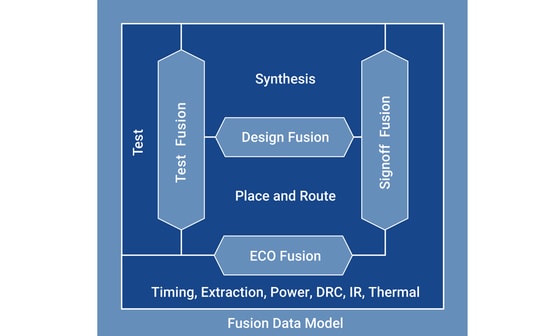

Synopsys is pretty well-known for their early entry into logic synthesis with the Design Compiler tool and more recent P&R tool with IC Compiler, so I met up with two folks at DAC to get a better idea of what this new Fusion technology was all about where the barriers between tools are changing. Michael Jackson and Rahul Deokar … Read More

Intel, Musk, and the Tweet That Launched a 1000 Ships on a Becalmed Sea