This is another installment covering TSMC’s very popular Open Innovation Platform event (OIP), held on August 25. This event presents a diverse and high-impact series of presentations describing how TSMC’s vast ecosystem collaborates with each other and with TSMC. Not all SerDes are the same. The presentation covered here,… Read More

UX in Agentic Systems. Innovation in VerificationA switch this month to principles behind building…Read More

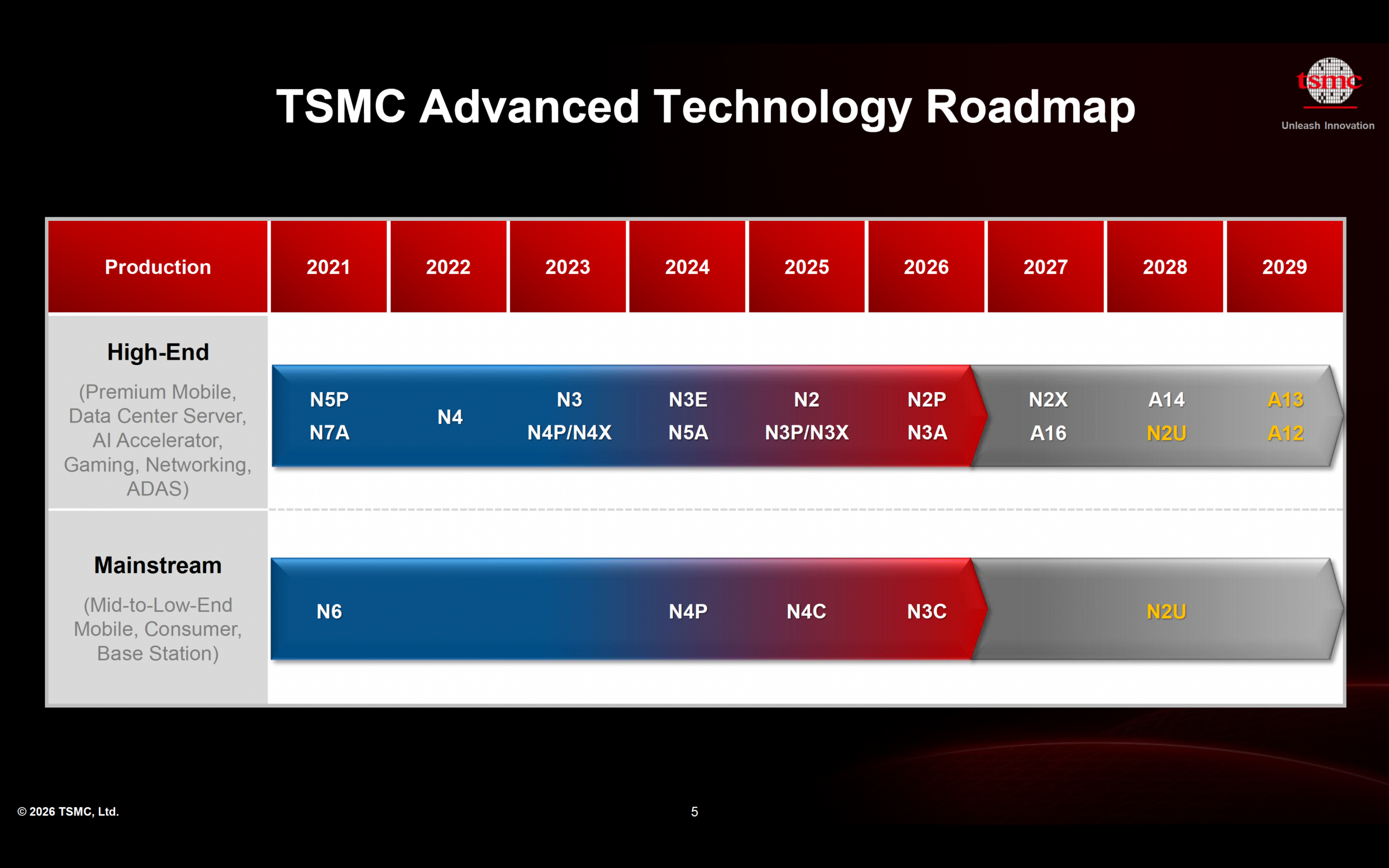

UX in Agentic Systems. Innovation in VerificationA switch this month to principles behind building…Read More The Shift to System-Level AI Drives Next-Generation SiliconAt its 2026 Technology Symposium, TSMC delivered a…Read More

The Shift to System-Level AI Drives Next-Generation SiliconAt its 2026 Technology Symposium, TSMC delivered a…Read More All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read More

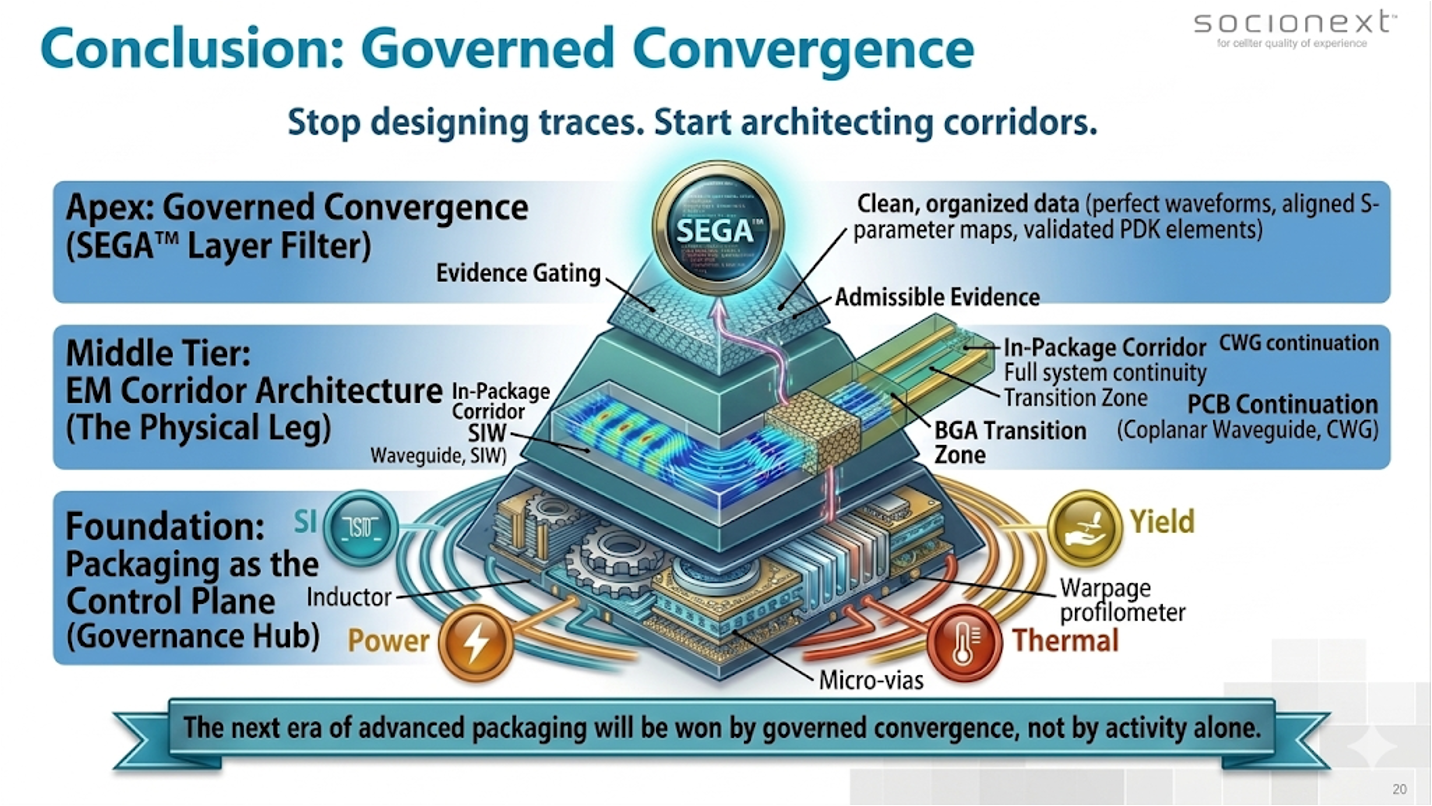

All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read More Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet GovernanceBy Dr. Moh Kolbehdari Dr. Moh Kolbehdari is…Read More

Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet GovernanceBy Dr. Moh Kolbehdari Dr. Moh Kolbehdari is…Read More SemiWiki Q&A with Julie Rogers, Executive Director, ESD AllianceThe Electronic System Design Alliance (ESD Alliance), a SEMI…Read More

SemiWiki Q&A with Julie Rogers, Executive Director, ESD AllianceThe Electronic System Design Alliance (ESD Alliance), a SEMI…Read MoreVerifying Warm Memory. Virtualizing to manage complexity

SSD memory is enjoying a new resurgence in datacenters through NVMe. Not as a replacement for more traditional HDD disk drives, which though slower are still much cheaper. NVMe storage has instead become a storage cache between hot DRAM memory close to processors and the “cold” HDD storage. I commented last year on why this has become… Read More

Update on Mentor’s Acquisition of Avatar Integrated Systems

Mentor Graphics, a Siemens Business, has completed their acquisition of EDA company Avatar Integrated Systems. I recently spoke with Joe Sawicki, Executive VP of the Mentor IC EDA segment, about the acquisition strategy and IC Design platform goals for integration of the Avatar products.

Avatar (formerly ATopTech) focused… Read More

Executive Interview: Vic Kulkarni of ANSYS

On the eve of the Innovative Designs Enabled by Ansys Semiconductor (IDEAS) Forum I spoke with Vic on a range of topics including his opening keynote: Accelerating Moore and Beyond Moore with Multiphysics. You can register here.

Vic Kulkarni is Vice President and Chief Strategist, Semiconductor Business Unit, Ansys, San Jose.… Read More

AI/ML SoCs Get a Boost from Synopsys IP on TSMC’s 7nm and 5nm

This is another installment covering TSMC’s very popular Open Innovation Platform event (OIP), held on August 25. This event presents a diverse and high-impact series of presentations describing how TSMC’s vast ecosystem collaborates with each other and with TSMC. The presentation covered here from Synopsys focuses on the… Read More

Bug Trace Minimization. Innovation in Verification

A checker tripped in verification. Is there a bug trace minimization technique to simplify manual debug? Paul Cunningham (GM, Verification at Cadence), Jim Hogan and I continue our series to highlight all the great research that’s out there in verification. Feel free to comment.

The Innovation

This month’s pick is Simulation-Based… Read More

WEBINAR: UVM RISC-V and DV

Oh, our semiconductor industry just loves acronyms, and the title of my blog packs three of the most popular acronyms together at once. I attended a webinar hosted by Aldec last week on this topic, “UVM Simulation-based environment for Ibex RISC-V CPU core with Google RISC-V DV“. Verification engineers have been … Read More

CEO Interview: Murilo Pilon Pessatti of Chipus Microelectronics

Murilo Pilon Pessatti is an Electrical Engineer with a MSEE in Analog IC design. He studied in Brazil at São Paulo University (USP) and earned a masters at Campinas State University (UNICAMP). Murilo then moved to Lisbon in Europe to work for ChipIdea, in the early 2000’s when the smartphone era was just taking off.

“I… Read More

From Moore’s Law to Moortec’s Law!

No-one likes being put on the spot and yet we all like a forecast…and as we all know, the only guarantee with a forecast is that it is wrong. Sports commentators have carved out a special niche for themselves with the ‘commentators curse’, just as they extol the virtues of an individual or a team, the sporting gods prove them wrong in … Read More

Protocol in Depth – Ethernet

Many times i notice people “kind of afraid” of some protocol, trying to avoid the usage because “it’s complicated”, I decide to go in-depth in one and show that maybe it’s not so complicated after all. First challenge is choosing the protocol and decide about the Ethernet, because this protocol… Read More

Solving the EDA tool fragmentation crisis