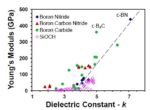

Of the three types of materials used in microelectronics – i.e., semiconductors, metals, and dielectrics – the first two often get the most attention. Yet, there is a pressing need for a rich variety of dielectric materials in device fabrication and interconnect isolation to satisfy the performance, power, and reliability … Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More

Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More

CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More

RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read More

Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read MoreAchronix Speedster7t Garners Best Practices Award for FPGA

FPGAs have played an important role in the growth of key markets, including networking, storage, mobile devices, etc. They offer a unique set of capabilities that ASICs, CPUs and GPUs find hard to match. FPGAs are wire-speed, programmable integrated circuits that accelerate data and applications. The ability to reprogram … Read More

Webinar: Rescale is Providing an On-Ramp to the Hybrid Cloud for Chip Design

We all know that design complexity is increasing at a fast pace. There’s always more analysis to run on larger and larger volumes of data. During tapeout, these demands can grow by an order of magnitude. Successful design projects need to add huge amounts of CPU, memory and storage for short bursts of time during tapeout to meet their… Read More

Car Wars 2021

A strange narrative took hold in the U.S. at the end of 2020 that vehicle sales were in decline, that cars weren’t selling. The reality is something quite different. In spite of nearly two solid months of auto factory and dealership shutdowns, automotive sales surged back in 2020 – a phenomenon that manifested globally with regional

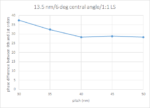

The Complexities of the Resolution Limits of Advanced Lithography

For advanced lithography used to shrink semiconductor device features according to Moore’s Law, resolution limits are an obvious consideration. It is often perceived that the resolution limit is simply derived from a well-defined equation, but nothing can be further from the truth.

Optical Lithography: the fine print

… Read MorePodcast EP2: Moore’s Law, Dead or Alive?

Dan and Mike are joined by Dr. Walden Rhines for a scenic tour of Moore’s Law. The genesis and evolution of Moore’s Law are discussed, along with the fundamental processes that have driven it. How the technology world continues to grow and innovate in spite of a slowing of Moore’s Law is a central theme of the discussion.… Read More

IEDM 2020 – Imec Plenary talk

On Monday morning at IEDM, Sri Samavedam of Imec opened the technical program with a plenary talk entitled “Future Logic Scaling: Towards Atomic Channels and Deconstructed Chips”. I am not generally a fan of plenary talks, I think the presenters often try to cover too much in their talks and end up not providing enough detail to be… Read More

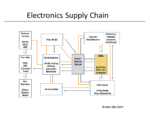

The Growing Chasm in Electronic System Design

Since the formation of the Electronic Design Automation (EDA) industry in the 1970s, Moore’s law has increased functionality onto a semiconductor die dramatically. In response, EDA tools for semiconductor design have also grown in functionality and the design processes for semiconductors have moved forward at a breakneck… Read More

Conference: Embedded DevOps

The catchy phrase DevOps is defined by Agile advocates as, “The practice of operations and development engineers participating together in the entire service lifecycle, from design through the development process to production support.”

I’ve been developing software since the stone ages, which means… Read More

Technology Optimization for Magnetoresistive RAM (STT-MRAM)

Spin-transfer torque magnetoresistive RAM (STT-MRAM) has emerged from several foundries as a very attractive IP option. An introduction to MRAM technology from GLOBALFOUNDRIES was provided in this earlier SemiWiki article. [1]

Briefly, STT-MRAM is a non-volatile storage option with the following attractive characteristics… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!