I remember it like it was yesterday. I was sitting at lunch with good friend Scott Santandrea, explaining my struggles to get traction with the sales channel for the Analog to Digital Converter product line I was managing. My business line had been spending a lot of resources developing high-performance 24-bit delta sigma and 20-bit

UX in Agentic Systems. Innovation in VerificationA switch this month to principles behind building…Read More

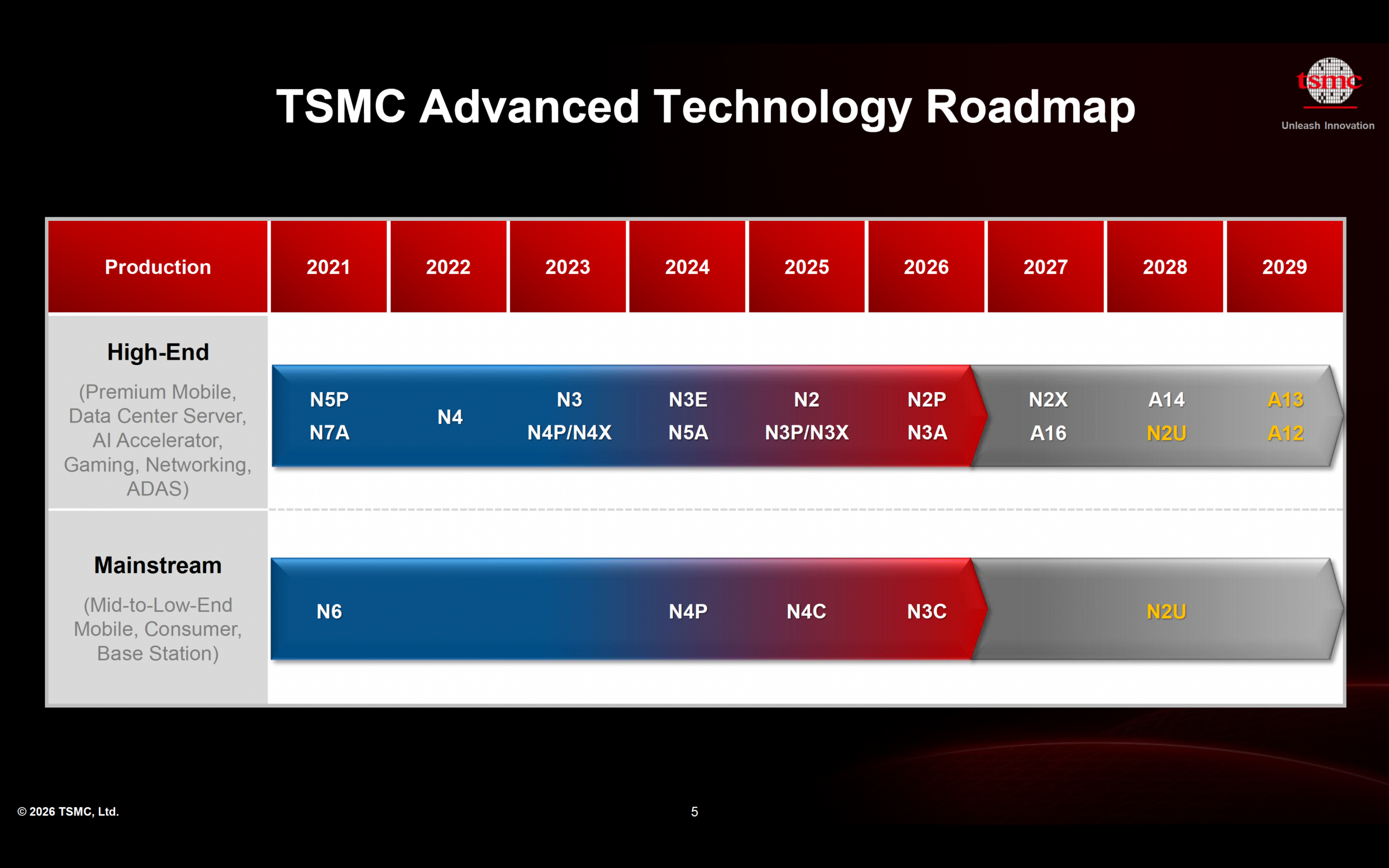

UX in Agentic Systems. Innovation in VerificationA switch this month to principles behind building…Read More The Shift to System-Level AI Drives Next-Generation SiliconAt its 2026 Technology Symposium, TSMC delivered a…Read More

The Shift to System-Level AI Drives Next-Generation SiliconAt its 2026 Technology Symposium, TSMC delivered a…Read More All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read More

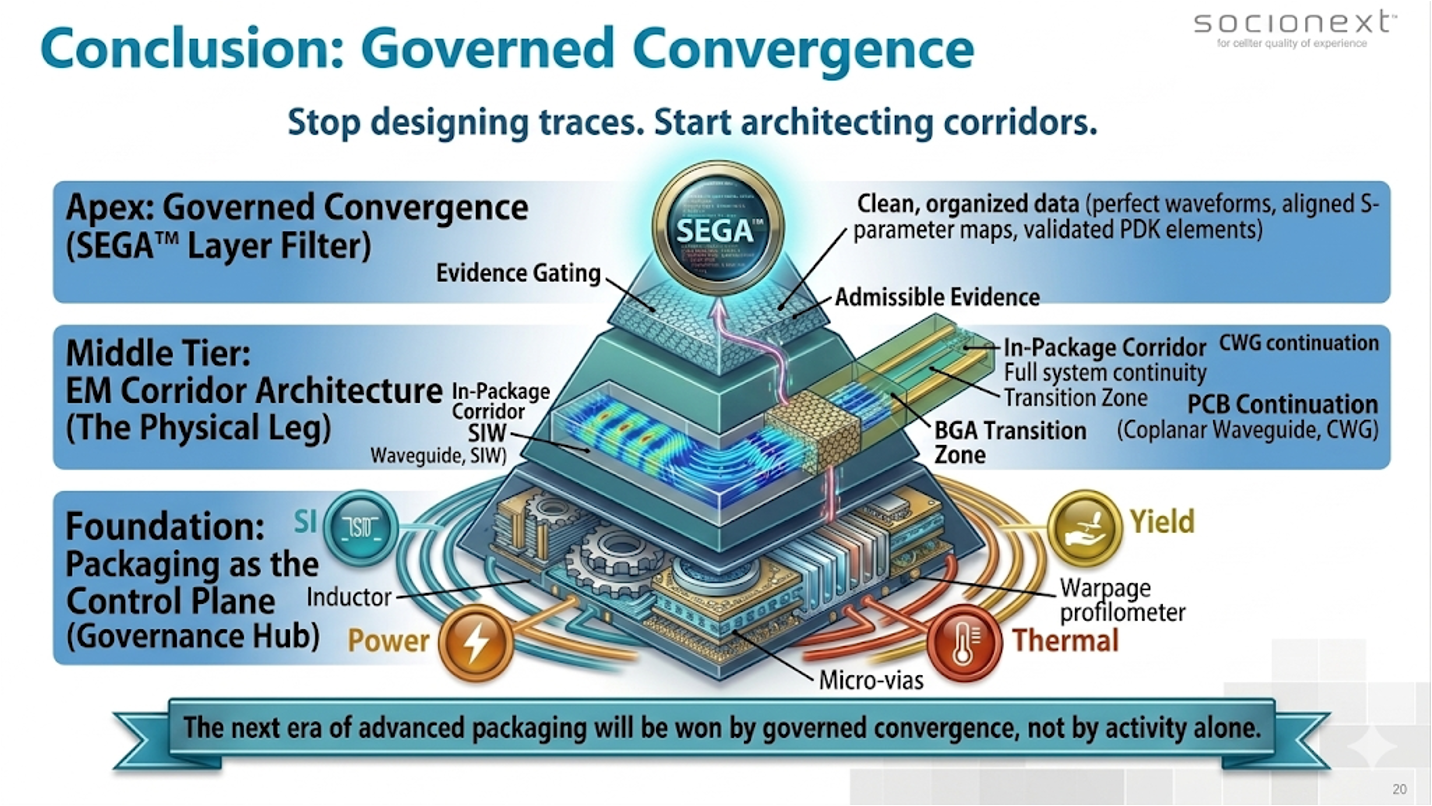

All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read More Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet GovernanceBy Dr. Moh Kolbehdari Dr. Moh Kolbehdari is…Read More

Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet GovernanceBy Dr. Moh Kolbehdari Dr. Moh Kolbehdari is…Read More SemiWiki Q&A with Julie Rogers, Executive Director, ESD AllianceThe Electronic System Design Alliance (ESD Alliance), a SEMI…Read More

SemiWiki Q&A with Julie Rogers, Executive Director, ESD AllianceThe Electronic System Design Alliance (ESD Alliance), a SEMI…Read MoreApple’s Priority On Improved OLED Encapsulation For Foldable Smartphones Will Impact Applied Materials

Smartphone shipments have been dropping over the past few years, as shown in Chart 1, as a result of several factors, but primarily the slowdown in smartphone innovation while at the same time prices have kept increasing. Even with the much anticipated 5G in 2020, unimpressive speed gains coupled with a Covid-19 backdrop, smartphones… Read More

Samtec Lets You Learn from Home with a Great Webinar Lineup

Work from home (WFH) has become a normal occurrence this past year. “Do you work from home?” “Of course, where else?” Samtec is taking the whole work from home thing up a notch with a new webinar lineup for 2021. Back by popular demand, they are launching a new series of educational webinars. Started last year, the gEEk SpEEk Webinar… Read More

2020 Retrospective. Innovation in Verification

Paul Cunningham (GM, Verification at Cadence), Jim Hogan and I launched our series on Innovation in Verification at the beginning of last year. We wanted to explore basic innovations and new directions researchers are taking for hardware and system verification. Even we were surprised to find how rich a seam we had tapped. We plan… Read More

The Spartan flow for custom silicon: when losing is NOT an option.

Every so often a custom silicon socket comes up at a system company that you simply cannot afford to lose if you’re a silicon supplier. These are the types of custom silicon sockets that last for generations of a product, in huge and predictable volumes, and for whatever reason they may become available. It’s not easy to predict… Read More

Automotive SoCs Need Reset Domain Crossing Checks

When the number of clock domain crossings (CDCs) in SoCs proliferated it readily became apparent that traditional verification methods were not well suited to ensuring that they were properly handled in the design. This led to the creation of new methods and tools to check for correct interfaces between domains. Now, in automotive… Read More

Siemens EDA is Applying Machine Learning to Back-End Wafer Processing Simulation

There’s a lot to unpack in the title of this post. First, Siemens EDA is the new name for Mentor, a Siemens Business. The organization continues to operate as part of Siemens Digital Industries Software. The organization has released a white paper that describes research done with the American University of Armenia. The work examines… Read More

Uber v Alto Ride Hail Streetfight

Uber, Lyft, Postmates, Instacart and Doordash were successful in their nearly $200M effort to pass California’s Proposition 22 in November – to allow gig operators to avoid treating their drivers as full-time employees with all of the associated employee benefits and legal protections. In the midst of a devastating pandemic… Read More

CES 2021 Goes All Digital

CES, the massive consumer technology show put on by the Consumer Technology Association (CTA), was held this week. Due to the global COVID-19 pandemic, CES 2021 was all digital. Last year, CES 2020 had over 170,000 attendees from over 160 countries and 4,400 exhibiting companies.

CES 2020 was held January 7-10, 2020 in Las Vegas,… Read More

CES 2021 and all things Cycling Technology

It’s January so time to give you another summary of what I’ve found at CES 2021 about new cycling products that have electronic content. During the pandemic in 2020 we’ve seen a surge in sales for bicycles, e-bikes, spin bikes and trainers as people wanted a simple way of getting around town running errands, or… Read More

Solving the EDA tool fragmentation crisis