When I think about servers and data centers, I think about multiple-core/high-power CPUs, Intel’s domination over the years and GPUs coming on strong in recent years. I think about very fast digital interfaces, such as PCI Express connections and the latest DDR memory interface. Precision analog isn’t something that first comes… Read More

UX in Agentic Systems. Innovation in VerificationA switch this month to principles behind building…Read More

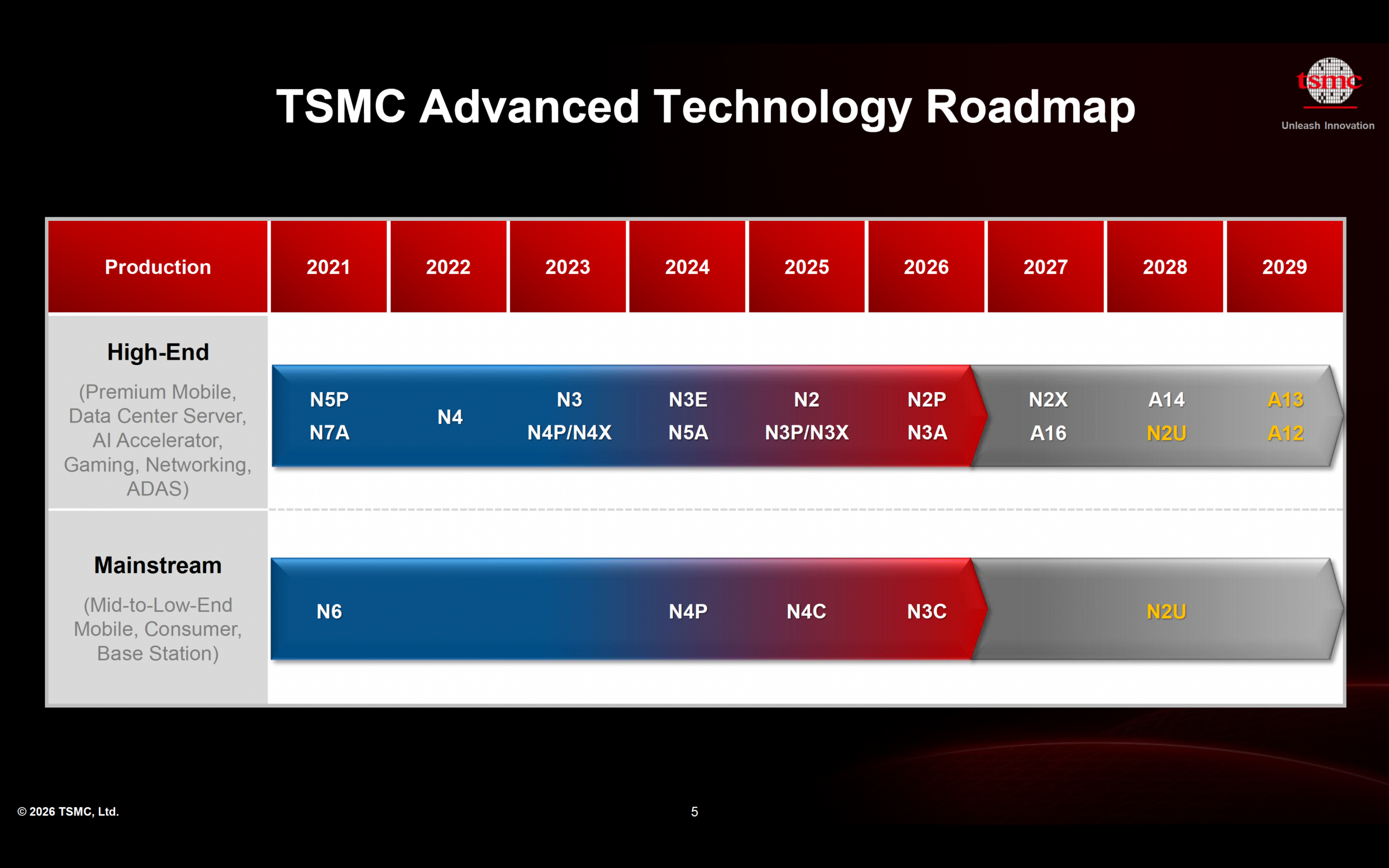

UX in Agentic Systems. Innovation in VerificationA switch this month to principles behind building…Read More The Shift to System-Level AI Drives Next-Generation SiliconAt its 2026 Technology Symposium, TSMC delivered a…Read More

The Shift to System-Level AI Drives Next-Generation SiliconAt its 2026 Technology Symposium, TSMC delivered a…Read More All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read More

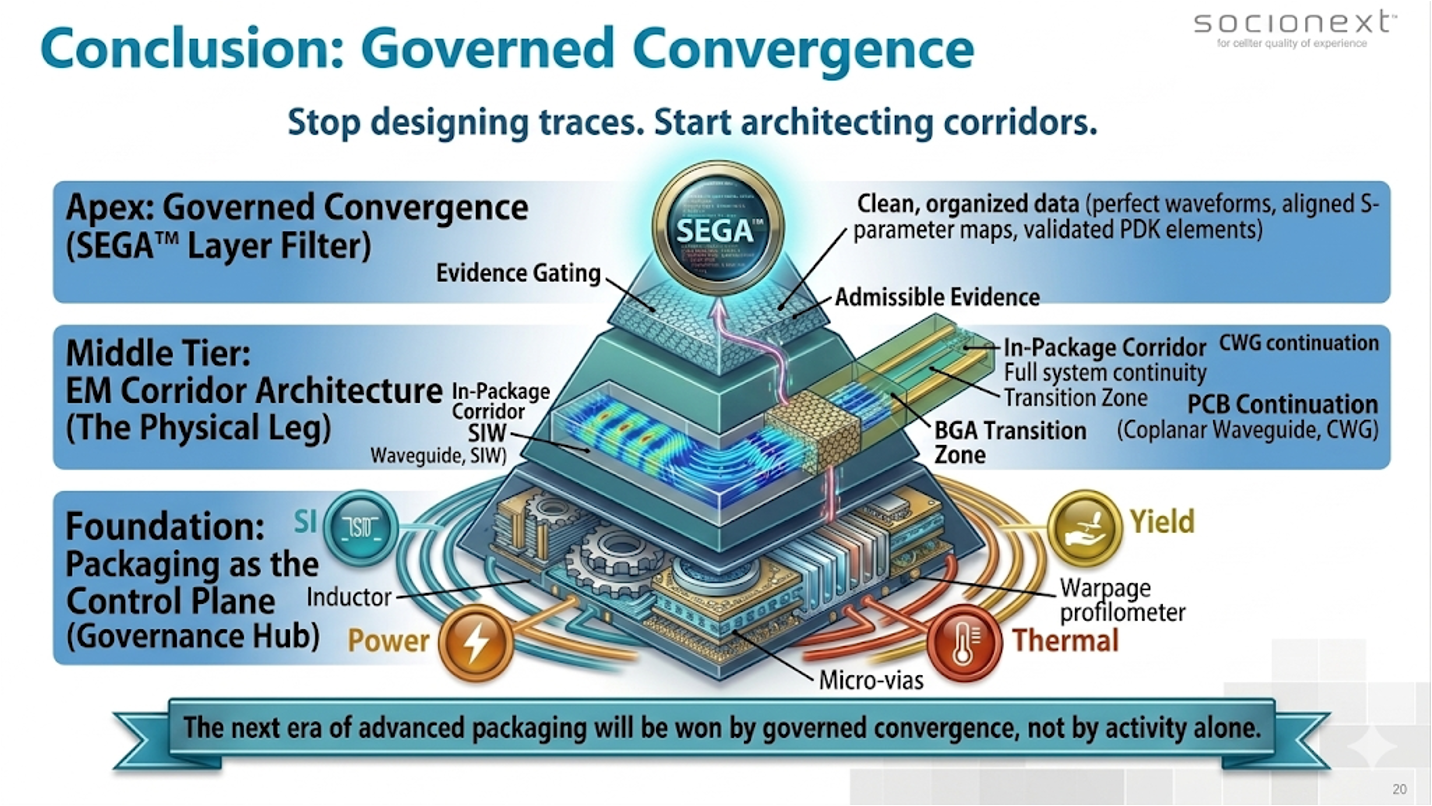

All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read More Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet GovernanceBy Dr. Moh Kolbehdari Dr. Moh Kolbehdari is…Read More

Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet GovernanceBy Dr. Moh Kolbehdari Dr. Moh Kolbehdari is…Read More SemiWiki Q&A with Julie Rogers, Executive Director, ESD AllianceThe Electronic System Design Alliance (ESD Alliance), a SEMI…Read More

SemiWiki Q&A with Julie Rogers, Executive Director, ESD AllianceThe Electronic System Design Alliance (ESD Alliance), a SEMI…Read MoreFalsely Vilifying Cryptocurrency in the Name of Cybersecurity

I get frustrated by shortsighted perceptions, which are misleading and dangerous is far easier to vilify something people don’t fully understand.

Here is another article, titled Bitcoin is Aiding the Ransomware Industry, published by Coindesk, implying cryptocurrency is the cause of digital crime.

This is one of many such… Read More

Trust, but verify. How to catch peanut butter engineering before it spreads into your system — Part 1: Validation.

I will address this topic with two blog posts: validation (i.e. post silicon) — Part 1, and verification (pre-silicon) — Part 2 (coming soon!). In this blog post, I will focus on validation.

One of the upsides of using catalog chips that have been in the market for a long time and have ramped in substantial volumes is that… Read More

Pitching Without a Net. Look Ma, No Slides!

It’s a given in the business world that whenever you need to communicate to a group you need a slide deck. Yet we vigorously agree that most pitches are miserably bad, for all the usual reasons. All about the presenter’s product, not audience needs. A firehose of technical detail designed to drown any possible objection. A script … Read More

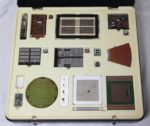

Examining a technology sample kit: IBM components from 1948 to 1986

I recently received a vintage display box used by IBM to illustrate the progress of computer technology. This display case, created by IBM Germany1 in 1986 included technologies ranging from vacuum tubes and magnetic core memory to IBM’s latest (at the time) memory chips and processor modules. In this blog post, I describe… Read More

How Airshield Can Save Transportation

The COVID-19 pandemic has devastated public transportation of every variety from buses and taxis to airplanes and trains. The combination of remote work and evolving economic shutdowns impacting restaurants, entertainment venues, schools, and tourism have sapped transportation demand while mitigation measures have reduced… Read More

Podcast EP5: Verification, Evolution and Revolution

Dan and Mike are joined by Dr. Bernard Murphy. Bernard has recently published a book on entrepreneurship and the importance of storytelling. In this podcast, Bernard talks about his journey from a PhD in Nuclear Physics at Oxford University to a storied career in EDA and verification. Bernard discusses a fundamental shift in… Read More

CEO Interview: Tuomas Hollman of Minima Processor

Tuomas is an experienced senior executive, with proficiency that ranges from strategy to product development and business management. He began his semiconductor industry career at Texas Instruments, serving for 15 years in increasingly important roles, including general management and profit and loss responsibility for… Read More

A Brief History of Perforce

In 2020 Perforce acquired Methodics, a provider of IP Lifecycle Management (IPLM) tools, and Daniel Nenni blogged about that in July 2020, but a lot has happened since Perforce was founded in 1995. In the beginning Christopher Seiwald founded Perforce in his Alameda basement based on his background as a software developer, and… Read More

Probing UPF Dynamic Objects

UPF was created to go beyond what HDL can do for managing on-chip power. HDLs are agnostic when it comes to dealing with supply & ground connections, power domains, level shifters, retention and other power management related elements of SoCs. UPF fills the breach allowing designers to specify in detail what parts of the design… Read More

Solving the EDA tool fragmentation crisis